- 您现在的位置:买卖IC网 > PDF目录16446 > CDB4265 (Cirrus Logic Inc)BOARD EVAL FOR CS4265 CODEC PDF资料下载

参数资料

| 型号: | CDB4265 |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 22/46页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS4265 CODEC |

| 标准包装: | 1 |

| 主要目的: | 音频编解码器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | CS4265 |

| 主要属性: | 立体声 24 位 192 kHz 采样率 |

| 次要属性: | 图形用户界面,S/PDIF/ I2S / I2C / SPI 接口 |

| 已供物品: | 板,缆线,CD |

| 产品目录页面: | 754 (CN2011-ZH PDF) |

| 相关产品: | CS4265-DNZR-ND - IC CODEC 24BIT 104DB 32-QFN CS4265-DNZ-ND - IC CODEC 24BIT 104DB 32-QFN 598-1039-ND - IC CODEC 24BIT 104DB 32QFN |

| 其它名称: | 598-1001 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

DS657F3

29

CS4265

clocking change, the DAC outputs will always be in a zero-data state. If non-zero serial audio input is

present at the time of switching, a slight click or pop may be heard as the DAC output automatically goes

to its zero-data state.

4.8

DAC Serial Data Input Multiplexer

The CS4265 contains a 2-to-1 serial data input multiplexer. This allows two separate data sources to be

input into the DAC without the use of any external multiplexing components. “Section 6.6.1 “DAC SDIN

Source (Bit 7)” on page 40” describes the control port settings necessary to control the multiplexer.

4.9

De-Emphasis Filter

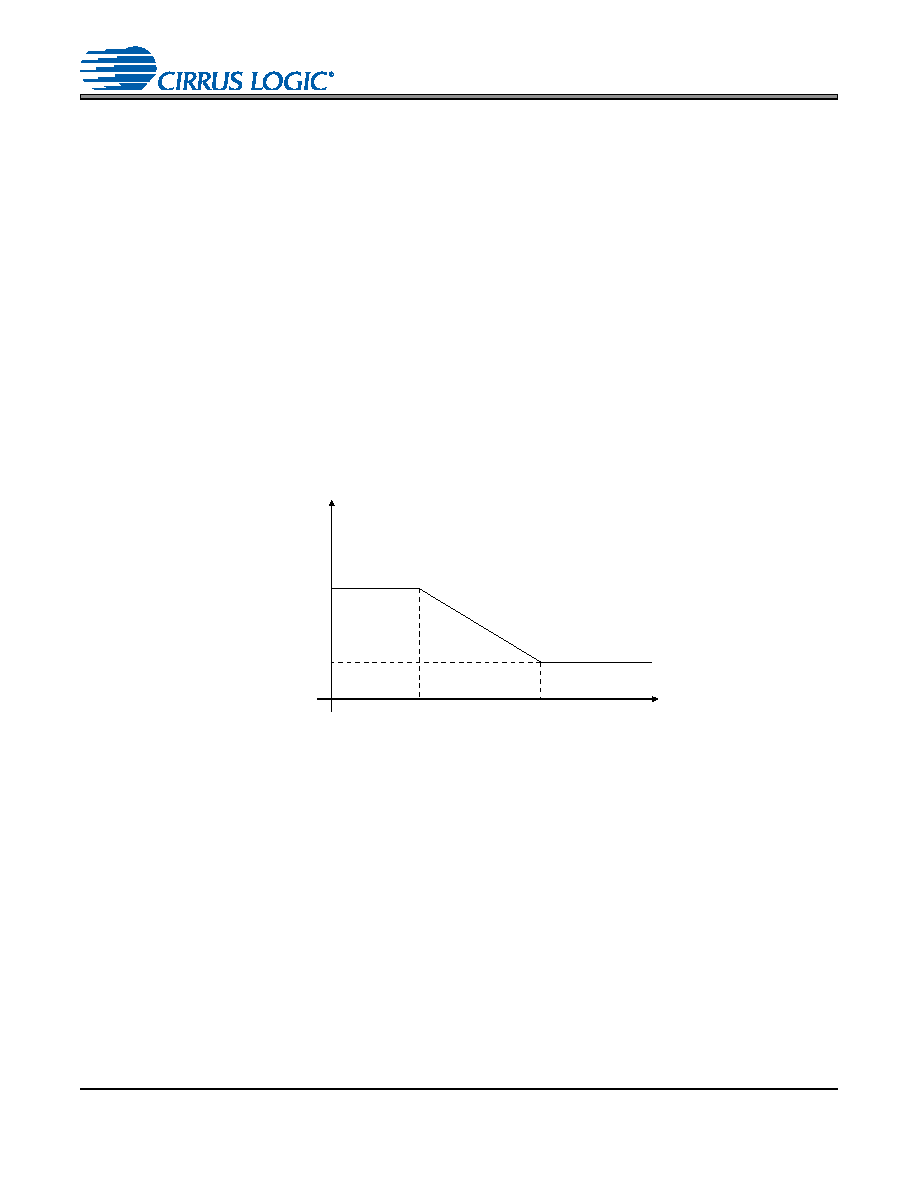

The CS4265 includes on-chip digital de-emphasis optimized for a sample rate of 44.1 kHz. The filter re-

sponse is shown in Figure 13. The frequency response of the de-emphasis curve scales proportionally with

changes in sample rate, Fs. Please see Section 6.3.3 “De-Emphasis Control (Bit 1)” on page 38 for de-em-

phasis control.

The de-emphasis feature is included to accommodate audio recordings that utilize 50/15 s pre-emphasis

equalization as a means of noise reduction.

De-emphasis is only available in Single-Speed Mode.

4.10

Internal Digital Loopback

The CS4265 supports an internal digital loopback mode in which the output of the ADC is routed to the input

of the DAC. This mode may be activated by setting the LOOP bit in the Signal Selection register (See “Signal

When this bit is set, the status of the DAC_DIF[1:0] bits in register 03h will be disregarded by the CS4265.

Any changes made to the DAC_DIF[1:0] bits while the LOOP bit is set will have no impact on operation until

the LOOP bit is cleared, at which time the Digital Interface Format of the DAC will operate according to the

format selected by the DAC_DIF[1:0] bits. While the LOOP bit is set, data will be present onthe SDOUT pin

in the format selected by the ADC_DIF bit in register 04h.

Gain

dB

-10dB

0dB

Frequency

T2 = 15 s

T1=50 s

F1

F2

3.183 kHz

10.61 kHz

Figure 13. De-Emphasis Curve

相关PDF资料 |

PDF描述 |

|---|---|

| 5070014034 | HEAT SHRINK TUBING |

| H3CKH-6018G | IDC CABLE - HKC60H/AE60G/HPK60H |

| 6278873-9 | C/A 50.125UM RIS MTRJ 9M1 |

| UPA1E182MHD1TO | CAP ALUM 1800UF 25V 20% RADIAL |

| 5070012033 | HEAT SHRINK TUBING |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB4270 | 功能描述:音频 IC 开发工具 Eval Bd 105dB 192kHz CODEC RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4271 | 功能描述:音频 IC 开发工具 Eval Bd CS4271 RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4272 | 功能描述:音频 IC 开发工具 Eval Bd CS4272 RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4299 | 功能描述:音频 IC 开发工具 Eval Bd AC’97 CODEC w/SRC RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB42L50 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Voltage, Stereo CODEC with headphone Amp |

发布紧急采购,3分钟左右您将得到回复。