- 您现在的位置:买卖IC网 > PDF目录16461 > CDB4955A (Cirrus Logic Inc)EVALUATION BOARD FOR CS4955A PDF资料下载

参数资料

| 型号: | CDB4955A |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 9/60页 |

| 文件大小: | 0K |

| 描述: | EVALUATION BOARD FOR CS4955A |

| 标准包装: | 1 |

| 主要目的: | 视频,视频处理 |

| 嵌入式: | 是,其它 |

| 已用 IC / 零件: | CS4955 |

| 主要属性: | NTSC/PAL 数字视频编码器 |

| 次要属性: | 图形用户界面,RS-232 接口 |

| 已供物品: | 板 |

| 相关产品: | CS4954-CQZR-ND - IC VID ENCODER NTSC/PAL 48-TQFP 598-1682-ND - IC VIDEO ENCODER NTSC/PAL 48TQFP |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

CS4954 CS4955

DS278F6

17

PROG_VS Register (0x0D). VSYNC can be de-

layed by thirteen lines or advanced by eighteen lines.

5.2.3 Vertical Timing

The CS4954/5 can be configured to operate in any

of four different timing modes: PAL, which is 625

vertical lines, 25 frames per second interlaced;

NTSC, which is 525 vertical lines, 30 frames per

second interlaced; and either 625 or 525 line Pseu-

do-Progressive Scan (See “Progressive Scan” on

page 18). These modes are selected in the

CONTROL_0 Register (0x00).

The CS4954/5 conforms to standard digital decom-

pression dimensions and does not process digital

input data for the active analog video half lines as

they are typically in the over/underscan region of

TV display. 240 active lines total per field are pro-

cessed for NTSC, and 288 active lines total per

field are processed for PAL. Frame vertical dimen-

sions are 480 lines for NTSC and 576 lines for

PAL. Table 2 specifies active line numbers for both

NTSC and PAL. Refer to Figure 6 for HSYNC,

VSYNC and FIELD signal timing.

5.2.4 Horizontal Timing

HSYNC is used to synchronize the horizontal-in-

put-to-output timing in order to provide proper hor-

izontal alignment. HSYNC defaults to an input pin

following RESET but switches to an output in Mas-

ter Mode (CONTROL_0 [4] = 1). Horizontal tim-

ing is referenced to HSYNC transitioning low. For

active video lines, digital video input is to be ap-

plied to the V [7:0] inputs for 244 (NTSC) or for

264 (PAL) CLK periods following the leading

(falling) edge of HSYNC if the PROG_HS Regis-

ters are set to default values.

5.2.5 NTSC Interlaced

The CS4954/5 supports NTSC-M, NTSC-J and

PAL-M modes where there are 525 total lines per

frame, two fixed 262.5-line fields per frame and 30

frames occurring per second. NTSC interlaced ver-

tical timing is illustrated in Figure 7. Each field

consists of one line for closed caption, 240 active

lines of video, plus 21.5 lines of blanking.

VSYNC field one transitions low at the beginning

of line four and will remain low for three lines or

2574 pixel cycles (858 × 3). The CS4954/5 exclu-

sively reserves line 21 of field one for closed cap-

tion insertion. Digital video input is expected to be

delivered to the CS4954/5 V [7:0] pins for 240

lines beginning on active video lines 22 and con-

tinuing through line 261. VSYNC field two transi-

tions low in the middle of line 266 and stays low for

three line-times and transitions high in the middle

of line 269. The CS4954/5 exclusively reserves line

284 of field two for closed caption insertion. Video

input on the V [7:0] pins is expected between lines

285 through line 525.

5.2.6 PAL Interlaced

The CS4954/5 supports PAL modes B, D, G, H, I,

N, and Combination N, in which there are 625 total

lines per frame, two fixed 312.5 line fields per

frame, and 25 total frames per second. Figure 8 il-

lustrates PAL interlaced vertical timing. Each field

consists of 287 active lines of video plus 25.5 lines

of blanking.

VSYNC will transition low to begin field one and

will remain low for 2.5 lines or 2160 pixel cycles

(864 × 2.5). Digital video input is expected to be

delivered to the CS4954/5 V [7:0] pins for 287

lines beginning on active video line 24 and continu-

ing through line 310.

Field two begins with VSYNC transitioning low

after 312.5 lines from the beginning of field one.

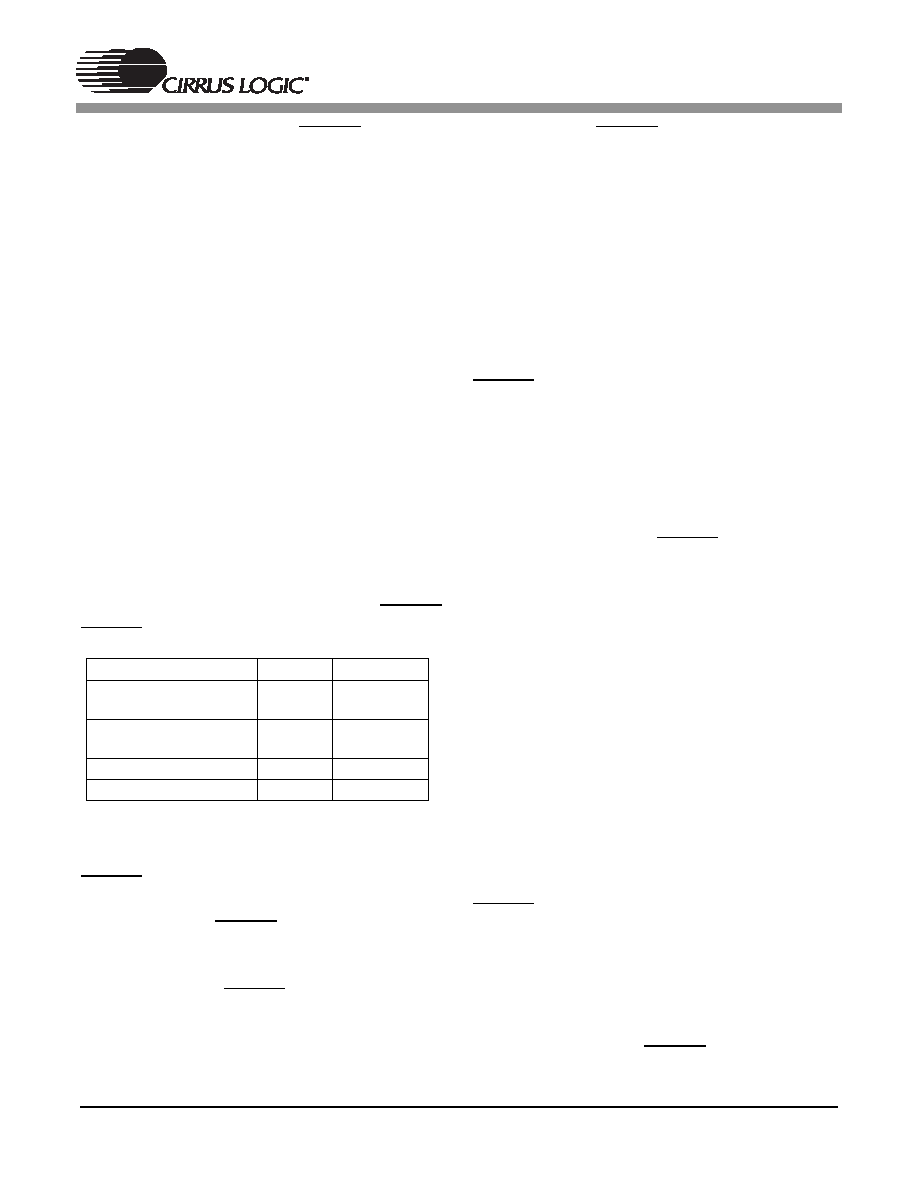

Mode

Field

Active Lines

NTSC

1, 3;

2, 4

22-261;

285-524

PAL

1, 3, 5, 7;

2, 4, 6, 8

23-310;

336-623

NTSC Progressive-Scan

NA

22-261

PAL Progressive-Scan

NA

23-310

Table 2. Vertical Timing

相关PDF资料 |

PDF描述 |

|---|---|

| VE-241-EX | CONVERTER MOD DC/DC 12V 75W |

| EB43-S0C2040X | CONN EDGEBOARD DUAL 40POS 3A |

| M3TTK-1436R | IDC CABLE - MSD14K/MC14M/MSD14K |

| GSM10DRTI-S13 | CONN EDGECARD 20POS .156 EXTEND |

| M3DYK-1006J | IDC CABLE - MKR10K/MC10G/MPD10K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB-496122-EV2 | 制造商:Cirrus Logic 功能描述: |

| CDB496122-EV2 | 功能描述:音频 IC 开发工具 Eval Bd CobraNet Trnspt/AdNtwrk Prcsr RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB49X | 制造商:Cirrus Logic 功能描述:EVAL BD - BASE BOARD FOR AUDIO DSP - Boxed Product (Development Kits) |

| CDB-5 | 功能描述:电线导管 5’ Brown RoHS:否 制造商:Panduit 类型:Slotted SideWall Open finger design wiring cut 材料:Polypropylene 颜色:Light Gray 大小: 最大光束直径: 抗拉强度: 外部导管宽度:25 mm 外部导管高度:25 mm |

| CDB5012 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Evaluation Board |

发布紧急采购,3分钟左右您将得到回复。