- 您现在的位置:买卖IC网 > PDF目录17021 > CDB5532U (Cirrus Logic Inc)BOARD EVAL FOR CS5532U ADC PDF资料下载

参数资料

| 型号: | CDB5532U |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 16/17页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS5532U ADC |

| 标准包装: | 1 |

| ADC 的数量: | 2 |

| 位数: | 24 |

| 采样率(每秒): | 3.84k |

| 数据接口: | 串行 |

| 输入范围: | ±2.5 V |

| 在以下条件下的电源(标准): | 35mW @ 3.84kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | CS5532 |

| 已供物品: | 板,缆线,CD |

| 相关产品: | CS5532-BSZR-ND - IC ADC 24BIT 2CH W/LNA 20-SSOP CS5532-ASZR-ND - IC ADC 24BIT 2CH W/LNA 20-SSOP 598-1113-5-ND - IC ADC 24BIT 2CH W/LNA 20SSOP 598-1112-5-ND - IC ADC 24BIT 2CH W/LNA 20SSOP |

| 其它名称: | 598-1159 |

IDT / ICS PCI EXPRESS JITTER ATTENUATOR

8

ICS9DB202CK-01 REV. B FEBRUARY 18, 2009

ICS9DB202-01

PCI EXPRESS JITTER ATTENUATOR

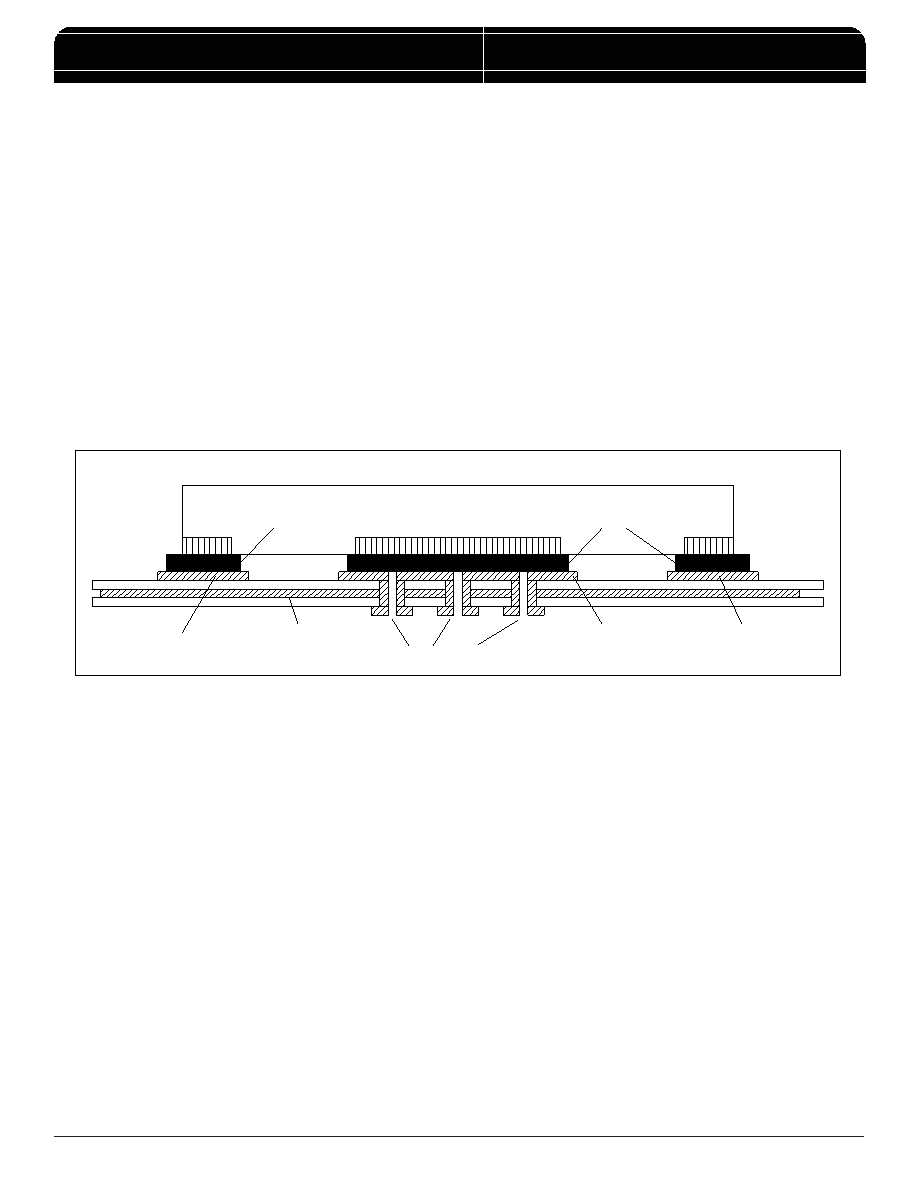

FIGURE 4. P.C.ASSEMBLY FOR EXPOSED PAD THERMAL RELEASE PATH –SIDE VIEW (DRAWING NOT TO SCALE)

VFQFN EPAD THERMAL RELEASE PATH

In order to maximize both the removal of heat from the package

and the electr ical perfor mance, a land patter n must be

incorporated on the Printed Circuit Board (PCB) within the footprint

of the package corresponding to the exposed metal pad or

exposed heat slug on the package, as shown in

Figure 4. The

solderable area on the PCB, as defined by the solder mask, should

be at least the same size/shape as the exposed pad/slug area on

the package to maximize the thermal/electrical performance.

Sufficient clearance should be designed on the PCB between the

outer edges of the land pattern and the inner edges of pad pattern

for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat

transfer and electrical grounding from the package to the board

through a solder joint, thermal vias are necessary to effectively

conduct from the surface of the PCB to the ground plane(s). The

land pattern must be connected to ground through these vias.

The vias act as “heat pipes”. The number of vias (i.e. “heat pipes”)

are application specific and dependent upon the package power

dissipation as well as electrical conductivity requirements. Thus,

thermal and electrical analysis and/or testing are recommended

to determine the minimum number needed. Maximum thermal

and electrical performance is achieved when an array of vias is

incorporated in the land pattern. It is recommended to use as

many vias connected to ground as possible. It is also

recommended that the via diameter should be 12 to 13mils (0.30

to 0.33mm) with 1oz copper via barrel plating. This is desirable to

avoid any solder wicking inside the via during the soldering process

which may result in voids in solder between the exposed pad/

slug and the thermal land. Precautions should be taken to

eliminate any solder voids between the exposed heat slug and

the land pattern. Note: These recommendations are to be used

as a guideline only. For further information, refer to the Application

Note on the

Surface Mount Assembly of Amkor’s Thermally/

Electr ically Enhance Leadframe Base Package, Amkor

Technology.

THERMAL VIA

LAND PATTERN

SOLDER

PIN

SOLDER

PIN PAD

PIN

GROUND PLANE

EXPOSED HEAT SLUG

(GROUND PAD)

相关PDF资料 |

PDF描述 |

|---|---|

| CDB5530U | BOARD EVAL FOR CS5530 |

| SIP4613ADVP-T1-E3 | IC LOAD SW HISIDE 1A SC75-6 |

| CDB5534U | EVAL BOARD FOR CS5534 |

| AD9648-125EBZ | EVAL BOARD AD9648-125 |

| CDB5463U-Z | EVAL BOARD USB FOR CS5463 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB5534U | 功能描述:数据转换 IC 开发工具 Eval Bd 24Bit ADC w/ Ultra Low-Noise USB RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| CDB5534U-Z | 功能描述:EVAL BD 24-BIT ADCS W/ULTRALN PG 制造商:cirrus logic inc. 系列:- 零件状态:在售 A/D 转换器数:1 位数:24 采样率(每秒):3.84k 数据接口:串行 输入范围:±2.5 V 不同条件下的功率(典型值):35mW @ 3.84kSPS 使用的 IC/零件:CS5534 所含物品:板,电缆 标准包装:1 |

| CDB5540 | 制造商:Cirrus Logic 功能描述:EVAL BOARD FOR CS5540 - Bulk |

| CDB5541 | 制造商:Cirrus Logic 功能描述:EVAL BOARD FOR 5540 & 5541 N/A - Bulk 制造商:Cirrus Logic 功能描述:Tools Development kit For Use |

| CDB5550 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Evaluation Board and Software |

发布紧急采购,3分钟左右您将得到回复。