参数资料

| 型号: | CDC2509BPW |

| 厂商: | Texas Instruments |

| 文件页数: | 8/14页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK DVR 3.3V 24-TSSOP |

| 标准包装: | 60 |

| 类型: | PLL 时钟驱动器 |

| PLL: | 带旁路 |

| 输入: | LVTTL |

| 输出: | LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:9 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 125MHz |

| 除法器/乘法器: | 无/无 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 880 (CN2011-ZH PDF) |

| 其它名称: | 296-20832-5 |

CDC2509B

3.3V PHASELOCK LOOP CLOCK DRIVER

SCAS613C SEPTEMBER 1998 REVISED DECEMBER 2004

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PACKAGE

TA

SMALL OUTLINE

(PW)

0

°C to 70°C

CDC2509BPWR

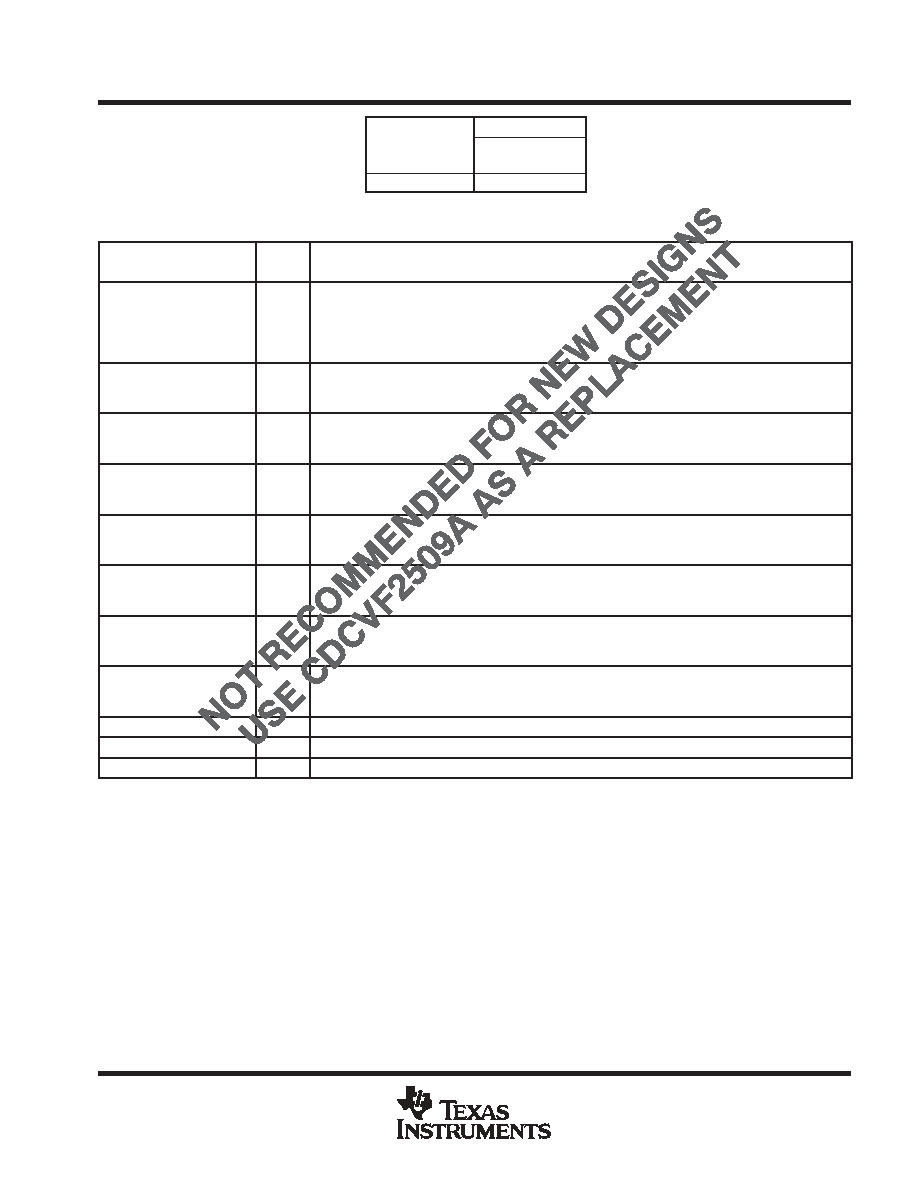

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

CLK

24

I

Clock input. CLK provides the clock signal to be distributed by the CDC2509B and the CDC2510B clock

drivers. CLK is used to provide the reference signal to the integrated PLL that generates the clock output

signals. CLK must have a fixed frequency and fixed phase for the PLL to obtain phase lock. Once the

circuit is powered up and a valid CLK signal is applied, a stabilization time is required for the PLL to

phase lock the feedback signal to its reference signal.

FBIN

13

I

Feedback input. FBIN provides the feedback signal to the internal PLL. FBIN must be hard-wired to

FBOUT to complete the PLL. The integrated PLL synchronizes CLK and FBIN so that there is nominally

zero phase error between CLK and FBIN.

1G

11

I

Output bank enable. 1G is the output enable for outputs 1Y(0:4). When 1G is low, outputs 1Y(0:4) are

disabled to a logic-low state. When 1G is high, all outputs 1Y(0:4) are enabled and switch at the same

frequency as CLK.

2G

14

I

Output bank enable. 2G is the output enable for outputs 2Y(0:3). When 2G is low, outputs 2Y(0:3) are

disabled to a logic low state. When 2G is high, all outputs 2Y(0:3) are enabled and switch at the same

frequency as CLK.

FBOUT

12

O

Feedback output. FBOUT is dedicated for external feedback. It switches at the same frequency as CLK.

When externally wired to FBIN, FBOUT completes the feedback loop of the PLL. FBOUT has an

integrated 25-

series-damping resistor.

1Y (0:4)

3, 4, 5, 8, 9

O

Clock outputs. These outputs provide low-skew copies of CLK. Output bank 1Y(0:4) is enabled via the

1G input. These outputs can be disabled to a logic-low state by deasserting the 1G control input. Each

output has an integrated 25-

series-damping resistor.

2Y (0:3)

16, 17, 20, 21

O

Clock outputs. These outputs provide low-skew copies of CLK. Output bank 2Y(0:3) is enabled via the

2G input. These outputs can be disabled to a logic-low state by deasserting the 2G control input. Each

output has an integrated 25-

series-damping resistor.

AVCC

23

Power

Analog power supply. AVCC provides the power reference for the analog circuitry. In addition, AVCC can

be used to bypass the PLL for test purposes. When AVCC is strapped to ground, PLL is bypassed and

CLK is buffered directly to the device outputs.

AGND

1

Ground

Analog ground. AGND provides the ground reference for the analog circuitry.

VCC

2, 10, 15, 22

Power

Power supply

GND

6, 7, 18, 19

Ground

相关PDF资料 |

PDF描述 |

|---|---|

| CDCLVP2104RHDR | IC CLOCK BUFFER 2:8 2GHZ 28-VQFN |

| CMP04FS | IC COMPARATOR QUAD LP 14-SOIC |

| CMP402GS-REEL | IC COMPARATOR LV 65NS 16-SOIC |

| CS3308-CQZ | IC ANLG VOL CTRL 8CH DGTL 48LQFP |

| CS3310-KSZR | IC DGTL VOL CTRL 2CH 16-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDC2509BPWG4 | 功能描述:时钟驱动器及分配 1-to-9 PLL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| CDC2509BPWLE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Nine Distributed-Output Clock Driver |

| CDC2509BPWR | 功能描述:时钟驱动器及分配 3.3V Clock RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| CDC2509BPWRG4 | 功能描述:时钟驱动器及分配 3.3V Clock RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| CDC2509BSTE-E | 功能描述:IC 3.3V PLL CLOCK DVR 24TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。