参数资料

| 型号: | CDCR83DBQ |

| 厂商: | Texas Instruments |

| 文件页数: | 14/16页 |

| 文件大小: | 0K |

| 描述: | IC DIRECT RAMBUS CLK GEN 24-QSOP |

| 标准包装: | 50 |

| 类型: | 时钟/频率发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 存储器,RDRAM |

| 输入: | TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 400MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 24-SSOP/QSOP |

| 包装: | 管件 |

| 产品目录页面: | 881 (CN2011-ZH PDF) |

| 其它名称: | 296-12165-5 |

CDCR83

DIRECT RAMBUS CLOCK GENERATOR

SCAS632B APRIL 2001 REVISED OCTOBER 2005

7

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

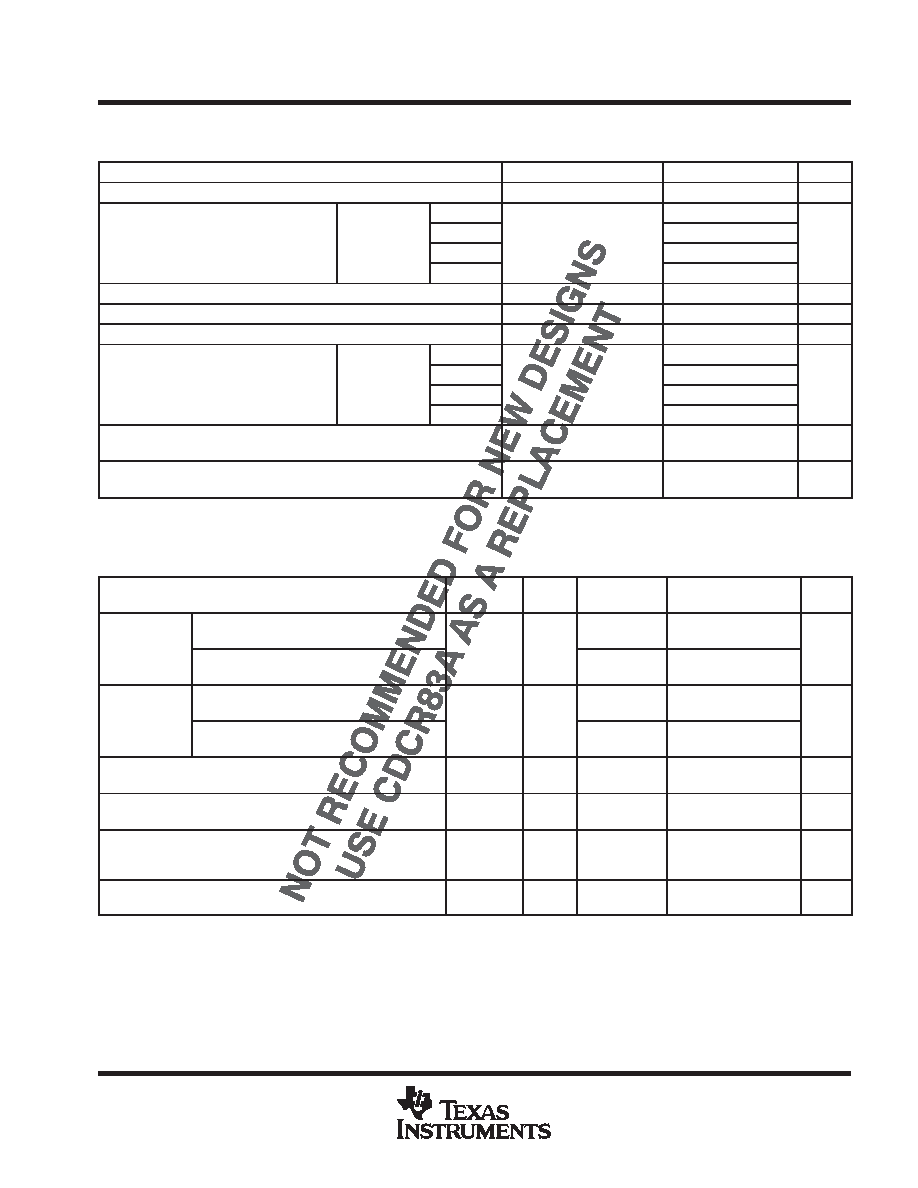

switching characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

tc(out)

Clock output cycle time

2.5

3.75

ns

Total cycle jitter over 1, 2,

Infinite and

267 MHz

80

t(jitter)

Total cycle jitter over 1, 2,

3, 4, 5, or 6 clock cycles

Infinite and

stopped phase

300 MHz

See Figure 3

70

ps

t(jitter)

3, 4, 5, or 6 clock cycles

stopped phase

alignment

356 MHz

See Figure 3

60

ps

alignment

400 MHz

50

t(phase)

Phase detector phase error for distributed loop

Static phase error}

100

ps

t(phase, SSC)

PLL output phase error when tracking SSC

Dynamic phase error}

100

ps

t(DC)

Output duty cycle over 10,000 cycles

See Figure 4

45%

55%

Infinite and

267 MHz

80

t(DC, err)

Output cycle-to-cycle

Infinite and

stopped phase

300 MHz

See Figure 5

70

ps

t(DC, err)

Output cycle-to-cycle

duty cycle error

stopped phase

alignment

356 MHz

See Figure 5

60

ps

duty cycle error

alignment

400 MHz

50

tr, tf

Output rise and fall times (measured at 20%80% of

output voltage)

See Figure 7

160

400

ps

t

Difference between rise and fall times on a single device

(20%80%) |tf tr|

See Figure 7

100

ps

All typical values are at VDD = 3.3 V, TA = 25°C.

Assured by design

state transition latency specifications

PARAMETER

FROM

TO

TEST

CONDITIONS

MIN

TYP

MAX

UNIT

t(powerup)

Delay time, PWRDNB

↑ to CLK/CLKB output

settled (excluding t(DISTLOCK))

Powerdown

Normal

See Figure 8

3

ms

t(powerup)

Delay time, PWRDNB

↑ to internal PLL and

clock are on and settled

Powerdown

Normal

3

ms

t(VDDpowerup)

Delay time, power up to CLK/CLKB output

settled

VDD

Normal

See Figure 8

3

ms

t(VDDpowerup)

Delay time, power up to internal PLL and

clock are on and settled

VDD

Normal

3

ms

t(MULT)

MULT0 and MULT1 change to CLK/CLKB

output resettled (excluding t(DISTLOCK))

Normal

See Figure 9

1

ms

t(CLKON)

STOPB

↑ to CLK/CLKB glitch-free clock

edges

CLK Stop

Normal

See Figure 10

10

ns

t(CLKSETL)

STOPB

↑ to CLK/CLKB output settled to

within 50 ps of the phase before STOPB was

disabled

CLK Stop

Normal

See Figure 10

20

cycles

t(CLKOFF)

STOPB

↓ to CLK/CLKB output disabled

Normal

CLK

Stop

See Figure 10

5

ns

All typical values are at VDD = 3.3 V, TA = 25°C.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-J51-MX-F3 | CONVERTER MOD DC/DC 12V 75W |

| SY88927VKC TR | IC RCVR 5V/3.3V 2.5GBPS 8-MSOP |

| SY88927VKC | IC RCVR 5V/3.3V 2.5GBPS 8-MSOP |

| MS3452W18-1S | CONN RCPT 10POS BOX MNT W/SCKT |

| SY10EP89VZI | IC DRVR COAX CABLE 3.3V/5V 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDCR83DBQG4 | 功能描述:时钟发生器及支持产品 400MHz Direct Rambus (TM) Clock Gen RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| CDCR83DBQR | 功能描述:时钟发生器及支持产品 400MHz Direct Rambus (TM) Clock Gen RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| CDCR83DBQRG4 | 功能描述:时钟发生器及支持产品 400MHz Direct Rambus (TM) Clock Gen RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| CDCS501 | 制造商:TI 制造商全称:Texas Instruments 功能描述:SSC Clock Generator/Buffer |

| CDCS501PW | 功能描述:时钟发生器及支持产品 Clock Driver w/ Opt Spread-Spect Clock RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。