- 您现在的位置:买卖IC网 > PDF目录16131 > CORR-8BIT-P2-U2 (Lattice Semiconductor Corporation)DEV IP CORE CORRELATOR ECP2 CONF PDF资料下载

参数资料

| 型号: | CORR-8BIT-P2-U2 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 4/10页 |

| 文件大小: | 0K |

| 描述: | DEV IP CORE CORRELATOR ECP2 CONF |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | CORR8BITP2U2 |

�� �

�

Lattice� Semiconductor�

�Correlator� IP� Core�

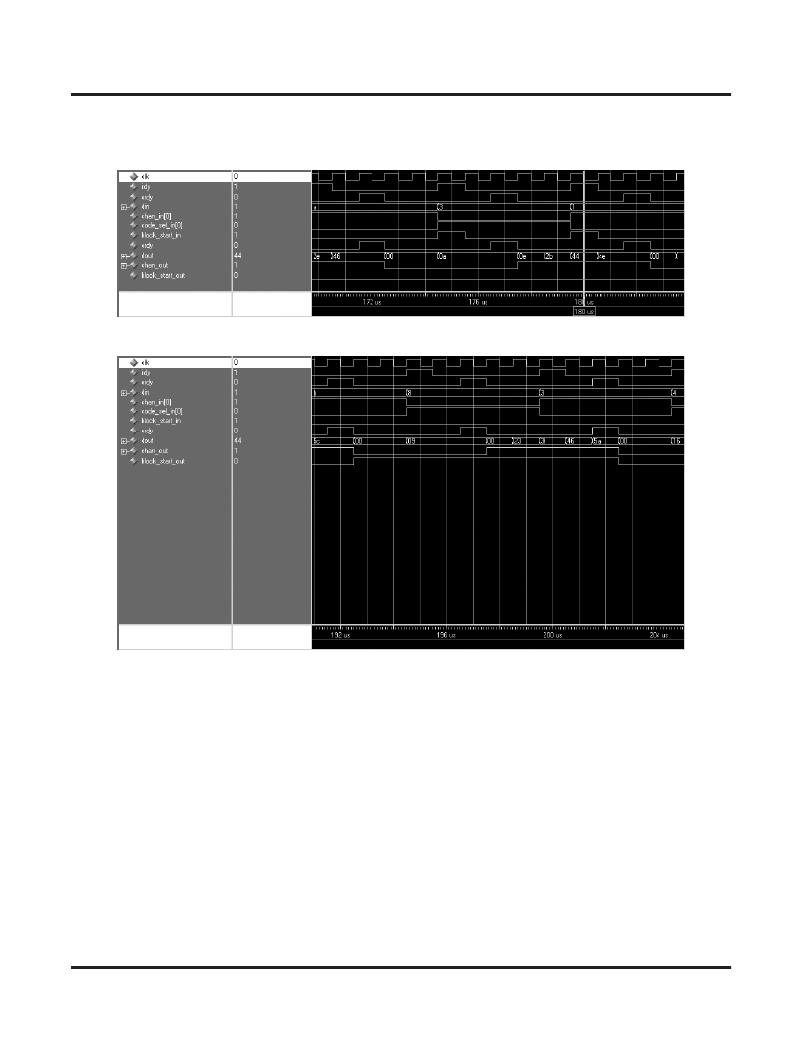

�In� this� example,� two� channels� and� two� different� coef?cient� sequences� have� been� con?gured.� Each� channel� can� be�

�correlated� to� either� of� the� two� coef?cient� sequences.�

�Figure� 2.� User� Interface� Timing� Diagram� for� Two-channel� Correlator�

�Figure� 3.� User� Interface� Timing� Diagram� for� Two-channel� Correlator�

�The� user� drives� the� irdy� signal� high� for� one� clock� cycle� indicating� that� the� input� values� are� valid.� Along� with� the�

�input� data,� the� user� also� sets� the� block_start_in� signal.� This� signal� will� be� taken� as� a� marker� by� the� Correlator�

�and� aligned� with� the� input� data� as� it� passes� through� the� Correlator� IP� core.� The� next� time� the� block_start_out�

�signal� is� set� and� chan_out� =� 0,� it� will� indicate� that� the� output� data� was� associated� with� this� input� data� value.� The�

�block_start� signals� act� as� markers� for� the� user� to� do� frame� alignments� between� the� input� and� outputs� of� the�

�Correlator� IP� core.� This� is� necessary� since� the� core� operates� on� one� input� data� sample� at� a� time.� It� does� not� per-�

�form� multiple� correlations� over� “num_lag”� values� as� expressed� in� Equation� 1.� This� allows� the� simplest� and� most�

�versatile� Correlator� IP� core� design.� If� it� is� necessary� to� operate� for� multiple� “lags,”� then� the� user� application� will�

�need� to� add� input� and� output� FIFOs� around� the� core� to� feed� data� values� one� sample� at� time.�

�At� time� 178.5μs,� crdy� again� goes� active� indicating� that� the� Correlator� IP� core� is� ready� to� accept� the� next� input�

�value,� and� in� the� example� of� Figure� 2� the� user� inputs� data� for� channel� 1.� At� time� 196.5μs,� the� correlation� result� for�

�channel� 0� is� ready� at� the� dout� outputs,� and� the� core� outputs� a� value� of� 0x9� on� dout� ,� sets� the� chan_out� to� 0,� and�

�asserts� the� ordy� signal.� It� also� asserts� the� block_start_out� signal� to� indicate� that� this� output� value� was� asso-�

�ciated� with� the� din� value� from� time� 175.5μs.�

�4�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6896PALT+T | IC SEQUENCE/SUPERVISOR 6UDFN |

| CORR-8BIT-E2-U2 | DEV IP CORE CORRELATOR EC/ECP |

| SPD74R-563M | INDUCTOR PWR SHIELDED 56UH SMD |

| MCP1316T-46FE/OT | IC SPRVSR SMPL RSET 4.6V SOT23-5 |

| CIC-FILT-XM-U2 | IP CORE CIC FILTER XP CONFIG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORR-8BIT-P2-UT2 | 功能描述:开发软件 8 BIT CORRELATOR IP RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-PM-U2 | 功能描述:开发软件 Correlator IP Core User Config RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-PM-UT2 | 功能描述:开发软件 8 BIT CORRELATOR IP RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-SC-U2 | 功能描述:开发软件 Correlator IP Core User Config RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-SC-UT2 | 功能描述:开发软件 8 BIT CORRELATOR IP RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。