- 您现在的位置:买卖IC网 > PDF目录16130 > CORR-8BIT-PM-U2 (Lattice Semiconductor Corporation)DEV IP CORE CORRELATOR ECP2M PDF资料下载

参数资料

| 型号: | CORR-8BIT-PM-U2 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 7/10页 |

| 文件大小: | 0K |

| 描述: | DEV IP CORE CORRELATOR ECP2M |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | CORR8BITPMU2 |

�� �

�

Lattice� Semiconductor�

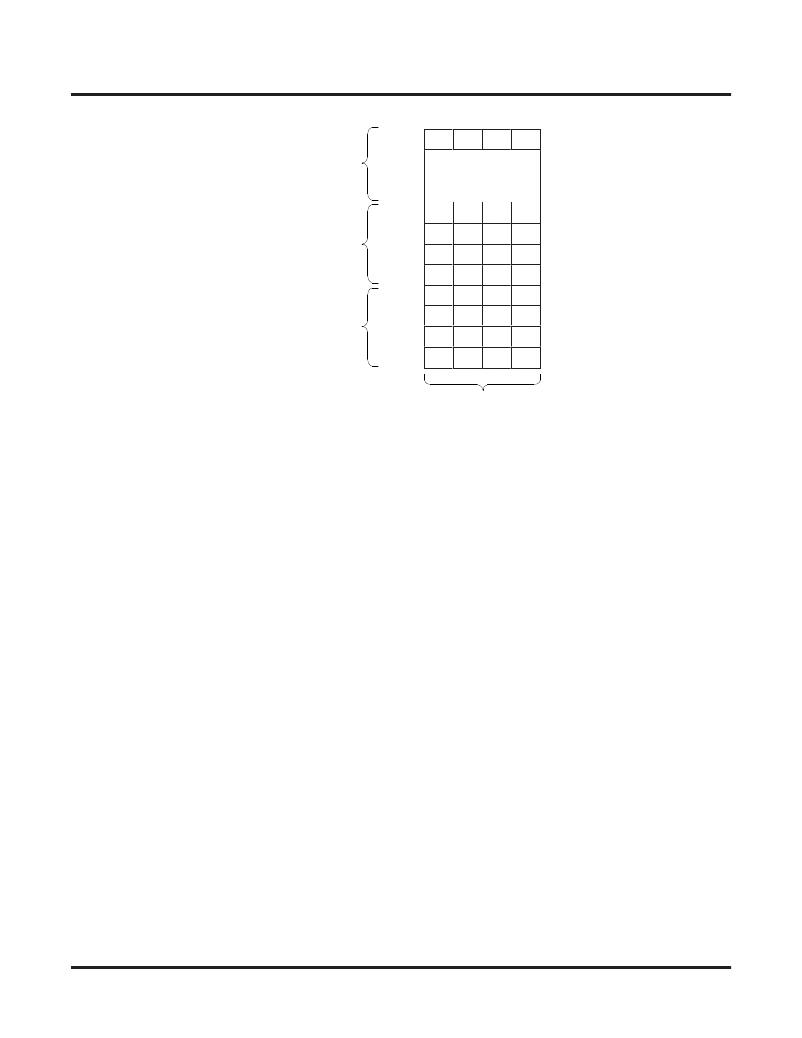

�Figure� 6.� Example� Coef?cient� Sequences� Written� in� Coef?cient� Memory�

�Upper� Locations�

�of� EBR� (Un� u� sed�

�in� this� Example)�

�Correlator� IP� Core�

�Ro� w� 7�

�0�

�0�

�0�

�0�

�Coefficient�

�Se� qu� ence� 1�

�Coefficient�

�Se� qu� ence� 0�

�Ro� w� 6�

�Ro� w� 5�

�Ro� w� 4�

�Ro� w� 3�

�Ro� w� 2�

�Ro� w� 1�

�Ro� w� 0�

�0�

�1�

�0�

�1�

�0�

�1�

�1�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�0�

�0�

�0�

�1�

�1�

�1�

�0�

�1�

�0�

�0�

�0�

�0�

�1�

�0�

�M� W� IDTH� w� ide�

�In� con?gurations� where� the� number� of� taps� is� not� a� power� of� 2,� the� coef?cient� sequences� will� need� to� be� padded�

�with� zeros� so� that� all� coef?cient� sequences� written� to� the� Coef?cient� Memory� are� a� power� of� 2� long.� This� is�

�because� the� Coef?cient� and� Tap� Memories� must� be� divided� up� evenly� into� sections� representing� the� individual�

�channels� and� coef?cient� sequences.� In� the� example� above,� if� the� number� of� taps� were� less� than� 16,� the� coef?cients�

�would� still� be� written� into� memory� the� same� way� except� that� padding� zeros� would� be� added� before� the� MSB.� The�

�padding� zeros� would� be� written� into� memory� starting� at� the� MSB� of� row� 3� for� coef?cient� sequence� 0.�

�Correlator� and� Adder/Accumulator� Blocks�

�The� Correlator� block� performs� the� multiplication� operations� in� Equations� 1� and� 2.� The� coef?cients� are� con?gured� by�

�the� user� to� be� either� unsigned� or� signed.� If� unsigned,� then� the� binary� coef?cient� values� simply� represent� {1,0}� and�

�the� multiplications� reduce� to� either� passing� the� tap� values� read� from� memory� to� the� Adder/Accumulator,� or� passing�

�a� zero� value.� If� the� coef?cients� are� signed,� then� the� binary� coef?cients� {1,0}� represent� values� of� {+1,-1}.� If� a� tap�

�value� is� multiplied� by� 1,� then� the� Correlator� block� does� nothing� other� than� pass� the� tap� value� read� from� memory� to�

�the� Adder/Accumulator.� If� a� tap� value� is� multiplied� by� -1,� then� the� Correlator� block� does� a� two’s� complement� conver-�

�sion� of� the� tap� value� read� from� memory� and� passes� the� result� to� the� Adder/Accumulator,� which� in� turn� completes�

�the� summation� of� the� correlation� sequence� to� generate� the� ?nal� result.�

�Decimation�

�The� Correlator� IP� core� allows� the� input� data� to� be� oversampled� from� two� to� eight� times� the� normal� sampling� rate.�

�The� OS_FACTOR� parameter� should� be� set� to� the� correct� oversampling� rate.� When� this� is� done,� the� core� will� auto-�

�matically� decimate� the� amount� of� data� which� is� included� in� the� correlation� operations� by� the� correct� amount.� For�

�example,� if� the� number� of� taps� is� eight� and� an� oversampling� rate� of� two� is� chosen,� then� the� circuit� will� correlate� the�

�eight� coef?cient� values� with� the� newest� input� tap� data� value� and� the� odd� numbered� tap� data� values� from� the� past�

�15� “old”� data� values.� The� correlation� will� look� like� this:�

�r� =� d1c1� +� d3c2� +� d5c3� +� d7c4� +� d9c5� +� d11c6� +� d13c7� +� d15c8�

�(4)�

�The� number� of� data� values� stored� in� Tap� Memory� for� a� given� channel� becomes� [OS_FACTOR*NUM_TAP],� or� in�

�this� case� 16.� The� number� of� coef?cients� per� channel� is� still� equal� to� NUM_TAP.�

�7�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBA28DTBN | CONN EDGECARD 56POS R/A .125 SLD |

| EBA28DTBH | CONN EDGECARD 56POS R/A .125 SLD |

| EBA28DTBD | CONN EDGECARD 56POS R/A .125 SLD |

| EBA28DTAN | CONN EDGECARD 56POS R/A .125 SLD |

| EBA28DTAH | CONN EDGECARD 56POS R/A .125 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORR-8BIT-PM-UT2 | 功能描述:开发软件 8 BIT CORRELATOR IP RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-SC-U2 | 功能描述:开发软件 Correlator IP Core User Config RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-SC-UT2 | 功能描述:开发软件 8 BIT CORRELATOR IP RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-X2-U2 | 功能描述:开发软件 Correlator IP Core User Config RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| CORR-8BIT-X2-UT2 | 功能描述:开发软件 BIT CORRELATOR IP RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。