参数资料

| 型号: | CP82C89 |

| 厂商: | Intersil |

| 文件页数: | 8/13页 |

| 文件大小: | 0K |

| 描述: | IC ARBITER BUS 5V 8MHZ 20-DIP |

| 标准包装: | 180 |

| 控制器类型: | CMOS 优先中断控制器 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 1mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 20-DIP(0.300",7.62mm) |

| 供应商设备封装: | 20-PDIP |

| 包装: | 管件 |

4

FN2980.2

February 27, 2006

Priority Resolving Techniques

Since there can be many bus masters on a multi-master

system bus, some means of resolving priority between bus

masters simultaneously requesting the bus must be

provided. The 82C89 Bus Arbiter provides several resolving

techniques. All the techniques are based on a priority

concept that at a given time one bus master will have priority

above all the rest. There are provisions for using parallel

priority resolving techniques, serial priority resolving

techniques, and rotating priority techniques.

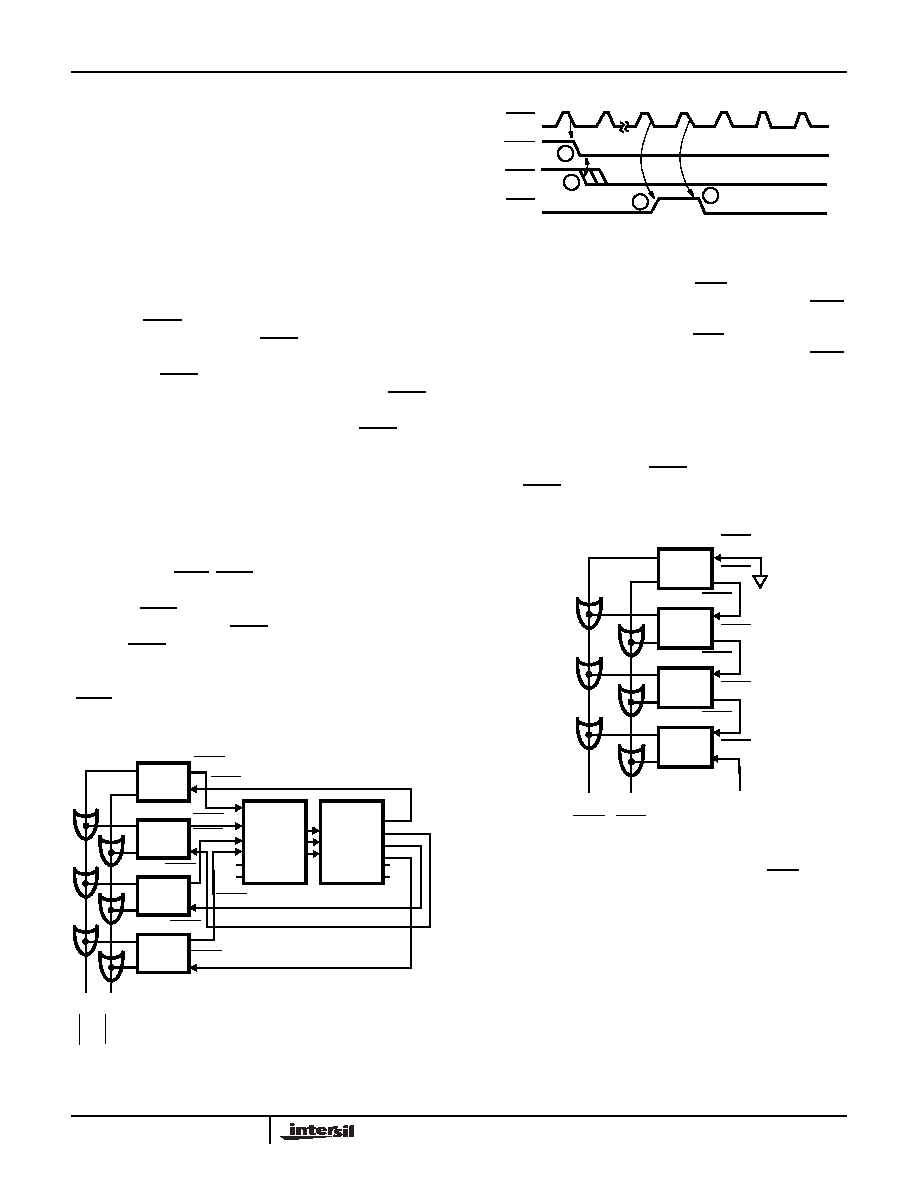

Parallel Priority Resolving

The parallel priority resolving technique uses a separate bus

request line BREQ for each arbiter on the multi-master

system bus, see Figure 1. Each BREQ line enters into a

priority encoder which generates the binary address of the

highest priority BREQ line which is active. The binary address

is decoded by a decoder to select the corresponding BPRN

(Bus Priority In) line to be returned to the highest priority

requesting arbiter. The arbiter receiving priority (BPRN true)

then allows its associated bus master onto the multi-master

system bus as soon as it becomes available (i.e., the bus is

no longer busy). When one bus arbiter gains priority over

another arbiter it cannot immediately seize the bus, it must

wait until the present bus transaction is complete. Upon

completing its transaction the present bus occupant

recognizes that it no longer has priority and surrenders the

bus by releasing BUSY. BUSY is an active low “OR” tied

signal line which goes to every bus arbiter on the system

bus. When BUSY goes inactive (high), the arbiter which

presently has bus priority (BPRN true) then seizes the bus

and pulls BUSY low to keep other arbiters off of the bus. See

waveform timing diagram, Figure 2. Note that all multimaster

system bus transactions are synchronized to the bus clock

(BCLK). This allows the parallel priority resolving circuitry or

any other priority resolving scheme employed to settle.

NOTES:

1. Higher priority bus arbiter releases BUSY.

2. Higher priority bus arbiter then acquires the bus and pulls BUSY

down.

3. Lower priority bus arbiter releases BUSY.

4. Higher priority bus arbiter then acquires the bus and pulls BUSY

down.

Serial Priority Resolving

The serial priority resolving technique eliminates the need

for the priority encoder-decoder arrangement by

daisychaining the bus arbiters together, connecting the

higher priority bus arbiter’s BPRO (Bus Priority Out) output

to the BPRN of the next lower priority. See Figure 3.

Rotating Priority Resolving

The rotating priority resolving technique is similar to that of

the parallel priority resolving technique except that priority is

dynamically re-assigned. The priority encoder is replaced by

a more complex circuit which rotates priority between

requesting arbiters thus allowing each arbiter an equal

chance to use the multi-master system bus, over time.

BUS

ARBITER

1

BUS

ARBITER

2

BUS

ARBITER

3

BUS

ARBITER

4

74HC148

PRIORITY

ENCODER

74HC138

3 TO 8

ENCODER

BREQ

BPRN

BREQ

BPRN

BREQ

BPRN

BREQ

BPRN

BUS

Y

CBRQ

FIGURE 1. PARALLEL PRIORITY RESOLVING TECHNIQUE

BCLK

BREQ

BPRN

BUSY

1

2

3

4

FIGURE 2. HIGHER PRIORITY ARBITER OBTAINING THE

BUS FROM A LOWER PRIORITY ARBITER

BUS

ARBITER

1

BUS

ARBITER

2

BUS

ARBITER

3

BUS

ARBITER

4

BPRN

BUSY

CBRQ

BPRO

BPRN

FIGURE 3. SERIAL PRIORITY RESOLVING

NOTE: The number of arbiters that may be daisy-chained together

in the serial priority resolving scheme is a function of BCLK and the

propagation delay from arbiter to arbiter. Normally, at 10MHz only 3

arbiters may be daisychained.

82C89

相关PDF资料 |

PDF描述 |

|---|---|

| CPC1465D | IC DC TERMINATION 16-SOIC |

| CPC1465M | IC SHDSL/ISDN DC TERM 16MLP |

| CPC2400E | MODULE MODEM 2400BAUD EMBEDDEDED |

| CPC5601D | IC DRVR PROGRAMMABLE 16-SOIC |

| CPC5710N | IC PHONE LINE MONITOR 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CP82C89S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CP82C89Z | 功能描述:输入/输出控制器接口集成电路 W/ANNEAL PERIPH BUS ARBITER 5V 8MHZ RoHS:否 制造商:Silicon Labs 产品: 输入/输出端数量: 工作电源电压: 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-64 封装:Tray |

| CP8300BT | 功能描述:IC MCU 制造商:cypress semiconductor corp 系列:* 零件状态:最後搶購 标准包装:1 |

| CP8300BTT | 功能描述:IC MCU 制造商:cypress semiconductor corp 系列:* 零件状态:最後搶購 标准包装:1 |

| CP8301AT | 功能描述:IC MCU 制造商:cypress semiconductor corp 系列:* 零件状态:最後搶購 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。