参数资料

| 型号: | CRD42L52 |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 8/28页 |

| 文件大小: | 0K |

| 描述: | REFERENCE DESIGN FOR CS42L52 |

| 标准包装: | 1 |

| 主要目的: | 音频编解码器 |

| 嵌入式: | 是,MCU,8 位 |

| 已用 IC / 零件: | CS42L52 |

| 主要属性: | 2 个立体声模拟输入,立体声线路和耳机输出,S/PDIF 发射器和接收器 |

| 次要属性: | 图形用户界面 |

| 已供物品: | 板,CD |

| 产品目录页面: | 755 (CN2011-ZH PDF) |

| 相关产品: | CS42L52-DNZR-ND - IC CODEC STER HDPN/SPKR 40-QFN CS42L52-DNZ-ND - IC CODEC STER HDPN/SPKR 40-QFN CS42L52-CNZR-ND - IC CODEC STER HDPN/SPKR 40-QFN 598-1628-ND - IC CODEC STER HDPN & SPKR 40QFN |

| 其它名称: | 598-1580 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

�

�CRD42L52�

�Table� 2� shows� expected� performance� characteristics� when� the� boards� are� configured� to� make� analog� input�

�to� digital� output� measurements.�

�Plot� Location�

�Dynamic� Range� -� Line� In� to� S/PDIF� Out�

��Frequency Response - Line In to S/PDIF Out� Figure 10 on page 15�

�THD� +� N� -� Line� In� to� S/PDIF� Out�

��Table� 2.� Line� In� to� S/PDIF� Out� Performance� Plots�

�3.3�

�S/PDIF� In� to� Speaker� Out�

�Stereo� differential� speaker� outputs� from� the� CS42L52� can� be� monitored� on� screw� terminals� J3� and� J4.� The�

�CS42L52� can� be� set� up� to� provide� data� to� the� PWM� modulator� for� producing� speaker� outputs� from� either�

�the� serial� port� PCM� input� or� the� ADC� output� using� the� FlexGUI� software.� For� a� description� of� the� Cirrus�

�FlexGUI� software� controls,� refer� to� Section� 4� on� page� 9� .� Table� 3� shows� expected� performance� characteris-�

�tics� when� the� boards� are� configured� to� make� speaker� output� measurements.�

�Plot� Location�

�Frequency Response - S/PDIF In to Speaker Out� Figure 17 on page 16�

�Table� 3.� S/PDIF� In� to� Speaker� Out� Performance� Plots�

�CRD42L52�

�R�

�T�

�CS42L52�

�(MASTER)�

�AIN1A�

�Line�

�Input�

�AIN1B�

�12.288� MHz�

�Oscillator�

�CS8416�

�S/PDIF� Rx�

�RMCK�

�SDOUT�

�LRCLK�

�SCLK�

�Headphone�

�R�

�T�

�HP/� LINE_OUTB�

�HP/� LINE_OUTA�

�MCLK�

�(MASTER)�

�Output�

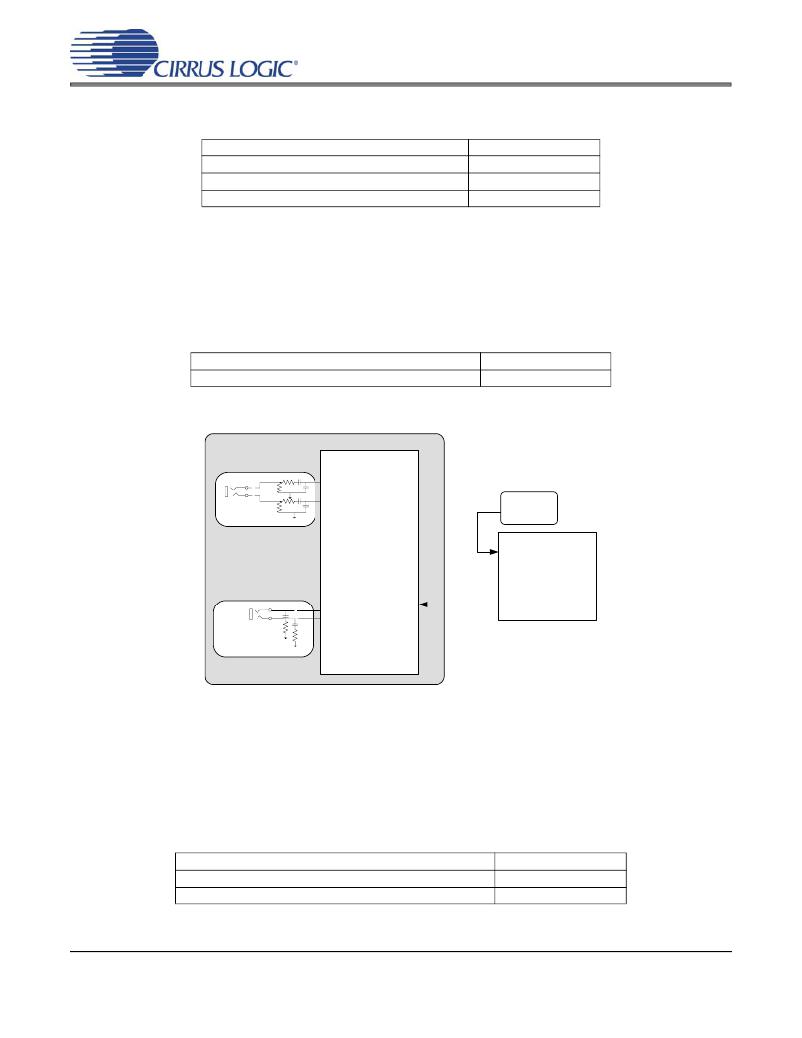

�Figure� 3.� CRD42L52� and� CDB42LDB1� Block� Diagram� for� Digital� Loopback� Testing�

�3.4�

�Analog� In� to� Analog� Out� -� Digital� Loopback�

�In� order� to� use� the� CS42L52� in� digital� loopback� mode,� one� can� configure� the� CS42L52� to� operate� in� master�

�or� slave� mode.� Figure� 3� shows� the� board� configuration� when� the� CODEC� is� set� up� to� operate� in� master�

�mode.� In� this� mode,� the� CS42L52� receives� an� MCLK� from� the� driver� board� from� the� CS8416� S/PDIF� reciev-�

�er.� As� described� in� Section� 1.3� on� page� 4� and� shown� in� Figure� 3� ,� the� S/PDIF� receiver� uses� the� on-board�

�12.288� MHz� clock� as� an� MCLK� when� it� is� not� receiving� a� S/PDIF� input� stream.� Table� 3� shows� expected� per-�

�formance� characteristics� when� the� boards� are� configured� to� make� speaker� output� measurements.�

�Plot� Location�

�Dynamic Range - Line In to HP Out (Digital Loopback)� Figure 18 on page 16�

�8�

�THD� +� N� -� Line� In� to� HP� Out� (Digital� Loopback)�

��DS680RD1�

�相关PDF资料 |

PDF描述 |

|---|---|

| CRDSB30WX2 | REF BD SPEAKERBAR MSA/DSP PARTS |

| CS-DF-MJB | RF CONN 2.4(IW 1501)STR JACK |

| CS-DM-MJB | RF CONN 2.4(IW 1501)STR PLUG |

| CS-FF-MJB | RF CONN 2.92(K)(IW 1501)STR JACK |

| CS-FF-MSB | RFCON 2.92(K)SEMF HP160 STR JACK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CRD4412 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:30 W Digital TV Amplifier with Integrated ADC |

| CRD4412A | 功能描述:音频 IC 开发工具 EvalBd 30W Qd Hlf- Brdg Dig Amp Pwr Stg RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CRD-4412A | 制造商:Cirrus Logic 功能描述:Digital Amplifier Evaluation B |

| CRD44130-FB | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:60 W Quad Half-Bridge Digital Amplifier Power Stage |

| CRD-44130-MIC | 制造商:Cirrus Logic 功能描述: |

发布紧急采购,3分钟左右您将得到回复。