- 您现在的位置:买卖IC网 > PDF目录380066 > CS4210 (National Semiconductor Corporation) IEEE 1394 OHCI Controller PDF资料下载

参数资料

| 型号: | CS4210 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | IEEE 1394 OHCI Controller |

| 中文描述: | 1394 OHCI控制器 |

| 文件页数: | 12/102页 |

| 文件大小: | 1571K |

| 代理商: | CS4210 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

www.national.com

12

Revision 1.0

G

Signal Definitions

(Continued)

2.2

SIGNAL DESCRIPTIONS

2.2.1

PCI Bus Interface Signals

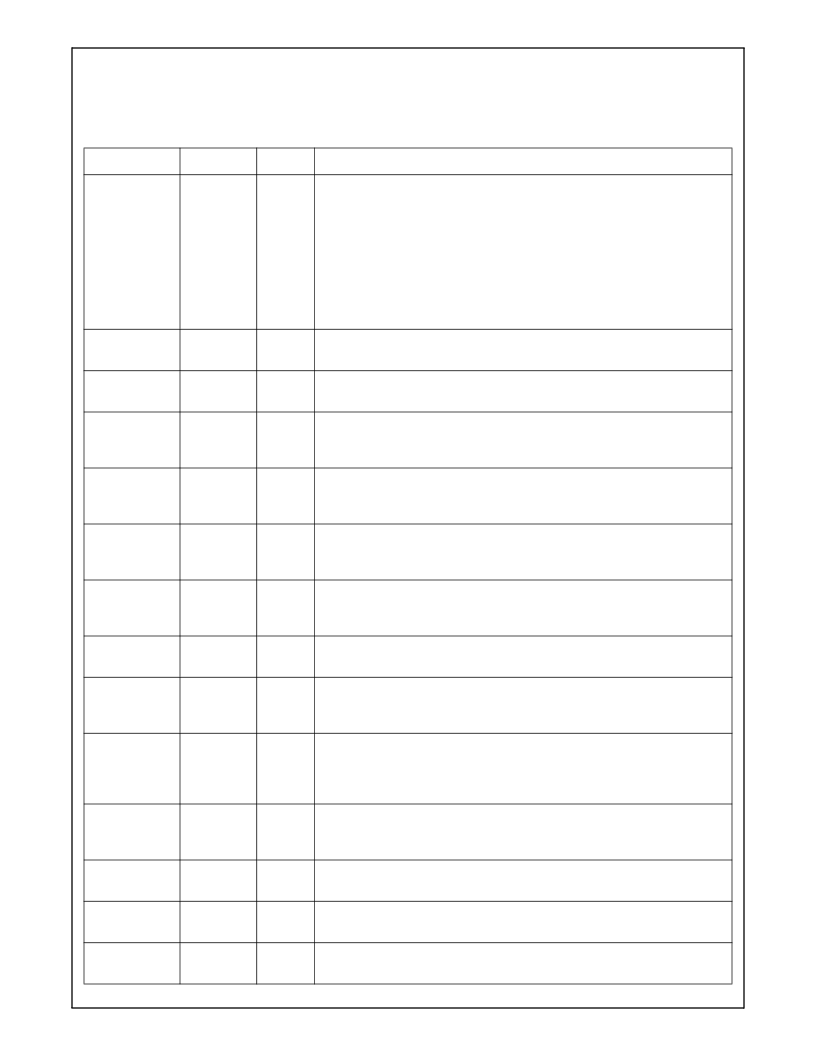

Signal Name

Pin No.

Type

Description

AD[31:0]

Refer to

Table 2-3

I/O

Multiplexed Address and Data

AD[31:0] is a physical address during the first clock of a PCI transaction; it is

the data during subsequent clocks.

When the CS4210 is a PCI master, AD[31:0] are outputs during the address

and write data phases, and are inputs during the read data phase of a trans-

action.

When the CS4210 is a PCI slave, AD[31:0] are inputs during the address

and write data phases, and are outputs during the read data phase of a

transaction.

C/BE[3:0]#

65, 53, 41,

28

I/O

Bus Command and Byte Enables

Multiplexed bus command and byte enables.

FRAME#

43

I/O

Cycle Frame

Driven by the initiator to indicate the beginning and duration of an access.

IRDY#

44

I/O

Initiator Ready

Indicates that the initiator is ready to complete the current data phase of the

transaction.

TRDY#

45

I/O

Target Ready

Indicates that the current data phase of the transaction is ready to be com-

pleted.

STOP#

48

I/O

Stop

Indicates that the current target is requesting the initiator to stop the current

transaction.

DEVSEL#

47

I/O

Device Select

When actively driven, DEVSEL# indicates the driving device has decoded

its address as the target of the current access.

IDSEL

29

I

Initialization Device Select

Used as a chip select during configuration read and write transactions.

PERR#

49

I/O

Parity Error

Used for reporting data parity errors during all PCI transactions except a

Special Cycle.

SERR#

51

I/O

System Error

Used for reporting address parity errors, data parity errors on the Special

Cycle command, or any other system error where the result will be cata-

strophic.

PAR

52

I/O

Parity

PAR is even parity across AD[31:0] and C/BE[3:0]. PAR is an input when

AD[31:0] are inputs and is an output when AD[31:0] are outputs.

PREQ#

15

O

PCI Bus Request

PCI bus request to PCI bus arbiter.

PGNT#

14

I

PCI Bus Grant

PCI bus grant from PCI bus arbiter.

INTA#

8

O

Interrupt A

1394 OpenHCI PCI interrupt.

相关PDF资料 |

PDF描述 |

|---|---|

| CS4210VJG | IEEE 1394 OHCI Controller |

| CS4215-KL | 16-Bit Multimedia Audio Codec |

| CS4215-KQ | 16-Bit Multimedia Audio Codec |

| CS4215 | 16-Bit Multimedia Audio Codec |

| CS4216 | 16-Bit Stereo Audio Codec |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4210A-CNZ | 制造商:Cirrus Logic 功能描述:IC LOW POWER HD AUDIO CODEC - Bulk 制造商:Cirrus Logic 功能描述:HD CODEC |

| CS4210A-CNZR | 功能描述:IC LOW POWER HD AUDIO CODEC RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:* 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| CS4210-CNZ | 制造商:Cirrus Logic 功能描述:IC LOW POWER HD AUDIO CODEC - Trays 制造商:Cirrus Logic 功能描述:IC Low Power HD Audio Codec |

| CS4210-CNZR | 制造商:Cirrus Logic 功能描述:IC LOW POWER HD AUDIO CODEC - Tape and Reel 制造商:Cirrus Logic 功能描述:IC Low Power HD Audio Codec |

| CS4210-CWZ | 制造商:Cirrus Logic 功能描述:IC Low Power HD Audio Codec |

发布紧急采购,3分钟左右您将得到回复。