- 您现在的位置:买卖IC网 > PDF目录380066 > CS4210 (National Semiconductor Corporation) IEEE 1394 OHCI Controller PDF资料下载

参数资料

| 型号: | CS4210 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | IEEE 1394 OHCI Controller |

| 中文描述: | 1394 OHCI控制器 |

| 文件页数: | 17/102页 |

| 文件大小: | 1571K |

| 代理商: | CS4210 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

Revision 1.0

17

www.national.com

G

Operational Description

(Continued)

3.2.3.3

Each of the eight implemented isochronous transmit and

each of the eight implemented isochronous receive con-

texts can generate an interrupt. Software can enable inter-

rupts on a per-context basis by setting the corresponding

IsochTxnContextIntMask or IsochRxnContextIntMask bit to

one. To efficiently handle interrupts which could conceiv-

ably be generated from eight different contexts in close

proximity to one another, there is a single bit for all IT DMA

contexts and another for all IR DMA contexts in the

CS4210 IntEvent register. These bits signify that at least

one but potentially several IT or IR DMA contexts

attempted to generate an interrupt. Software can read the

isochTxIntEvent register to find out which isochronous

transmit context(s) are involved. Software can read the Iso-

Isoch Tx and Rx Context Interrupts

chRxIntEvent register to find out which isochronous receive

context(s) are involved.

Table 3-4 shows a map of the IsochTx/Rx Context Interrupt

Event and Mask Set/Clear registers. Refer to Section

4.4.16.4 on page 73 through Section 4.4.16.7 on page 74

for further register information.

The number of supported isochronous DMA contexts var-

ies for 1394 OHCI implementations from a minimum of four

to a maximum of 32. Software can determine the number

of

supported

IT

or

IR

FFFF_FFFFh to IsochTxIntMask register for IT and Isoch-

RxIntMask register for IR, and then reading it back. Bits

returned as 1’s indicate supported contexts, and bits

returned as 0’s indicate unsupported/unimplemented con-

texts.

DMA

contexts

by

writing

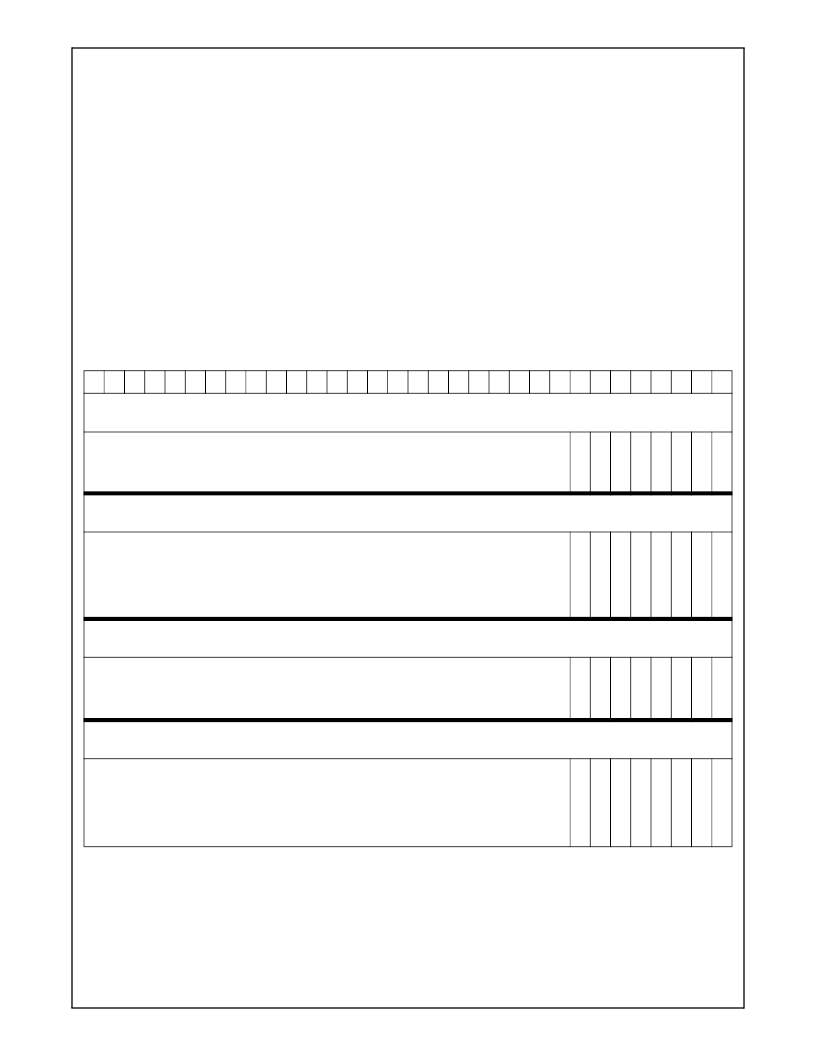

Table 3-4. IsochTx and IsochRx Context Interrupt Related Registers

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

BAR0+Offset 90h

BAR0+Offset 94h

IsochTxIntEvent Set Register

IsochTxIntEvent Clear Register

RSVD

i

i

i

i

i

i

i

i

BAR0+Offset 98h

BAR0+Offset 9Ch

IsochTxIntMask Set Register

IsochTxIntMask Clear Register

RSVD

i

i

i

i

i

i

i

i

BAR0+Offset A0h

BAR0+Offset A4h

IsochRxIntEvent Set Register

IsochRxIntEvent Clear Register

RSVD

i

i

i

i

i

i

i

i

BAR0+Offset A8h

BAR0+Offset ACh

IsochRxIntMaskSet Register

IsochRxIntMaskClear Register

RSVD

i

i

i

i

i

i

i

i

相关PDF资料 |

PDF描述 |

|---|---|

| CS4210VJG | IEEE 1394 OHCI Controller |

| CS4215-KL | 16-Bit Multimedia Audio Codec |

| CS4215-KQ | 16-Bit Multimedia Audio Codec |

| CS4215 | 16-Bit Multimedia Audio Codec |

| CS4216 | 16-Bit Stereo Audio Codec |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4210A-CNZ | 制造商:Cirrus Logic 功能描述:IC LOW POWER HD AUDIO CODEC - Bulk 制造商:Cirrus Logic 功能描述:HD CODEC |

| CS4210A-CNZR | 功能描述:IC LOW POWER HD AUDIO CODEC RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:* 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| CS4210-CNZ | 制造商:Cirrus Logic 功能描述:IC LOW POWER HD AUDIO CODEC - Trays 制造商:Cirrus Logic 功能描述:IC Low Power HD Audio Codec |

| CS4210-CNZR | 制造商:Cirrus Logic 功能描述:IC LOW POWER HD AUDIO CODEC - Tape and Reel 制造商:Cirrus Logic 功能描述:IC Low Power HD Audio Codec |

| CS4210-CWZ | 制造商:Cirrus Logic 功能描述:IC Low Power HD Audio Codec |

发布紧急采购,3分钟左右您将得到回复。