- 您现在的位置:买卖IC网 > PDF目录380066 > CS4216 (Cirrus Logic, Inc.) 16-Bit Stereo Audio Codec PDF资料下载

参数资料

| 型号: | CS4216 |

| 厂商: | Cirrus Logic, Inc. |

| 元件分类: | Codec |

| 英文描述: | 16-Bit Stereo Audio Codec |

| 中文描述: | 16位立体声音频编解码器 |

| 文件页数: | 14/58页 |

| 文件大小: | 799K |

| 代理商: | CS4216 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

frequency. SM2 is similar to SM1 except that

CLKIN is not used and SCLK becomes the mas-

ter clock and is fixed at 256

×

Fs. SM3 was

designed as an easy interface to general purpose

DSPs and provides extra features such as one

more bit of attenuation, a master mode, and vari-

able frame sizes. SM4 is similar to SM3 but

splits the audio data from the control data

thereby reducing the audio serial bus bandwidth

by half. The control data is transmitted through a

control serial port in SM4.

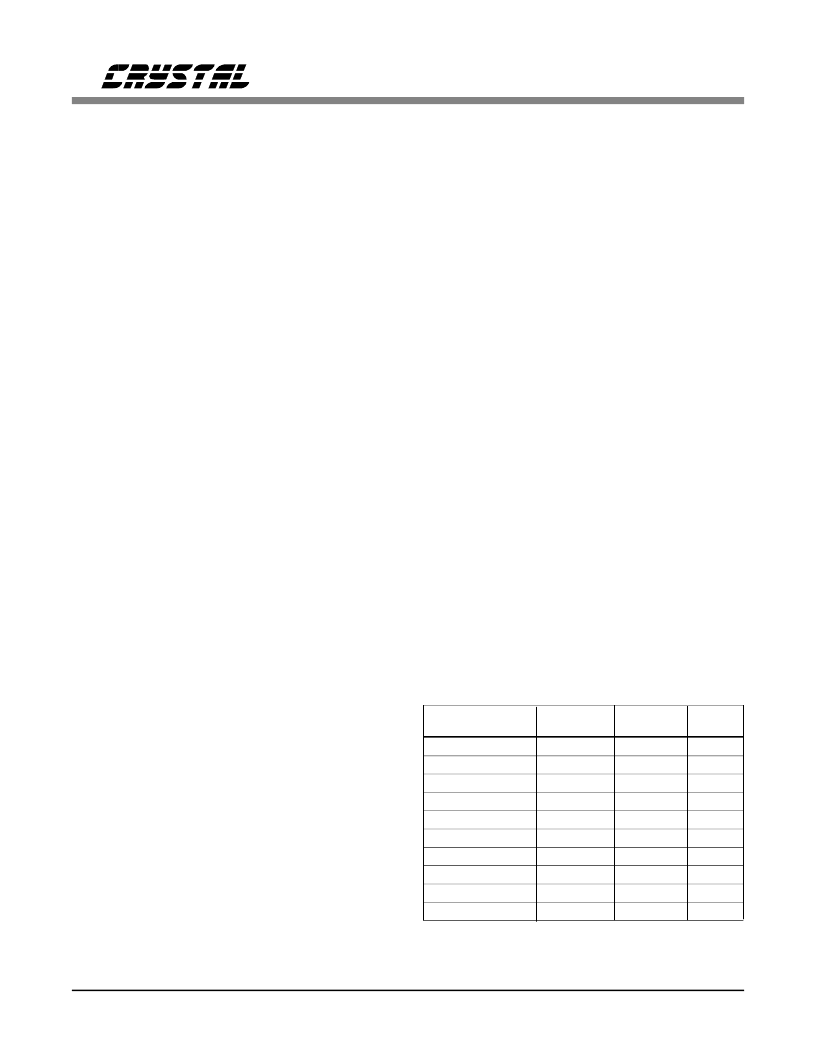

Table 1 lists the serial port modes available,

along with some of the differences between

modes. The first three columns in Table 1 select

the serial mode. The "SCLK Bit Center" column

indicates whether SCLK is rising or falling in

the center of a bit period. The "Sub-frame

Width" column indicates how many bits are in

an individual codec’s sub-frame. SM4 differs

from all other modes by separating the control

data from the audio data. In both SM1 and SM2,

there are 256 bits per frame which allows up to

four codecs to occupy the same bus. In SM3 and

SM4, the number of bits per frame is program-

mable. In SM1 and SM2, SCLK and SSYNC

must be generated externally; whereas, in SM3

and SM4 the CS4216 can optionally generate

those signals. In all modes, SCLK and SSYNC

must be synchronous to the master clock. The

last column in Table 1 lists the master frequency

used by the codec. In SM1, the master fre-

quency, input on CLKIN, is 512 times the

highest sample frequency available. In SM2, the

master frequency is fixed at 256 times the sam-

ple frequency and, in this mode, SCLK is the

master clock. In SM3, the master frequency is

256 times the highest frequency available and is

input on CLKIN or SCLK, based on the sub-

mode used. In SM4, the master frequency is also

256 times the highest frequency available and is

input on CLKIN.

SERIAL MODE 1, SM1

Serial Mode 1 is a slave mode selected by set-

ting SMODE3 = SMODE2 = SMODE1 = 0.

SCLK and SYNC must be synchronous the mas-

ter clock. SM1 uses a two bit wide (minimum)

frame sync with an optional word sync. In this

mode, SSYNC low for one SCLK period fol-

lowed by SSYNC high for a minimum of two

SCLK periods indicates the beginning of a

frame. The first bit of the frame starts with the

rising edge of SSYNC. An optional word sync,

being one SCLK period high, may be used to

indicate the start of a new 32-bit word. Figures 5

and 6 contain the serial data format for SM1. In

this serial mode, the ratio of two clocks are used

to select sample frequency. These are the master

clock CLKIN and the serial clock SCLK.

CLKIN should be set to 512

×

Fs

max

, where

Fs

max

is the maximum required sample rate.

SCLK must be externally set to a value of

CLKIN/N, such that SCLK equals 256 times the

desired sample rate. The codec uses the ratio be-

tween CLKIN and SCLK to set the internal

sample frequency and causes the CS4216 to go

into soft power down mode if the SCLK fre-

quency drops to <CLKIN/12. Even if only 1

CS4216 is used, the timing for 4 devices must be

maintained. Table 2 shows some example sample

rates for SM1.

Sample Rate

kHz

48

32

24

19.2

16

12

9.6

8

7.2

44.1

SCLK

MHz

12.288

8.192

6.144

4.9152

4.096

3.072

2.4576

2.048

1.843

11.2896

CLKIN

MHz

24.576

24.576

24.576

24.576

24.576

24.576

24.576

24.576

22.116

22.5792

N

2

3

4

5

6

8

10

12

12

2

Table 2. SM1 - Example Clock Frequencies

CS4216

14

DS83F2

相关PDF资料 |

PDF描述 |

|---|---|

| CS4216-KL | IC EEPROM SRL 256-8BIT 8DIP |

| CS4216-KQ | 16-Bit Stereo Audio Codec |

| CS4218-KL | 16-Bit Stereo Audio Codec |

| CS4218-KQ | 16-Bit Stereo Audio Codec |

| CS4218 | 16-Bit Stereo Audio Codec |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4216-KL | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS4216-KQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4217-KL | 制造商:CRYSTAL 功能描述: |

| CS4218 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

| CS4218-KL | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-Bit Stereo Audio Codec |

发布紧急采购,3分钟左右您将得到回复。