- 您现在的位置:买卖IC网 > PDF目录380066 > CS4222-KS (CIRRUS LOGIC INC) 20-Bit Stereo Audio Codec with Volume Control PDF资料下载

参数资料

| 型号: | CS4222-KS |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 20-Bit Stereo Audio Codec with Volume Control |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封装: | SSOP-28 |

| 文件页数: | 14/26页 |

| 文件大小: | 580K |

| 代理商: | CS4222-KS |

Serial Audio Data Interface

Serial Audio Interface Signals

The serial interface clock, SCLK, is used for

transmitting and receiving audio data. The active

edge of SCLK is chosen by setting the DSCK bit

in the DSP Port Mode Byte (#6); the default

upon power-up is that data is valid on the rising

edge for both input and output. SCLK is an in-

put from an external source and at least 20

SCLK’s per half period of LRCK are required

for proper operation.

The Left/Right clock (LRCK) is used to indicate

left and right data and the start of a new sample

period. The frequency of LRCK must be equal

to the system sample rate, Fs.

SDIN is the data input pin which drives a pair of

DACs. SDOUT is the output data pin from the

ADC’s.

Serial Audio Interface Formats

The serial audio port supports 5 input and 2 out-

put formats, shown in Figures 6 and 7. These

formats are chosen through the DSP Port Mode

Byte (#5) with the DDO and DDI2/1/0 bits. The

data output format is 20 bits and may be left jus-

tified or I

2

S compatible depending on the state

of the DDO bit. The input data format is set

with the DDI bits to be left or right justified or

I

2

S compatible. In addition, the polarity of the

SCLK edge used to clock in/out data from the

CS4222 may be set via the DSCK bit in the DSP

Port Mode Byte (#5). The default input and out-

put format is I

2

S compatible.

Control Port Interface

The control port is used to load all the internal

settings. The operation of the control port may

be completely asynchronous with the audio sam-

ple rate. However, to avoid potential interference

problems, the control port pins should remain

static if no operation is required.

The control port has 2 modes: SPI and I

2

C

,

with the CS4222 operating as a slave device. If

I

2

C operation is desired, AD0/CS should be tied

to VD or DGND. If the CS4222 ever detects a

negative transition on AD0/CS after power-up,

SPI mode will be selected.

SPI Mode

In SPI mode, CS is the CS4222 chip select sig-

nal, CCLK is the control port bit clock, CDIN is

the input data line from the microcontroller and

the chip address is 0010000. All signals are in-

puts and data is clocked in on the rising edge of

CCLK.

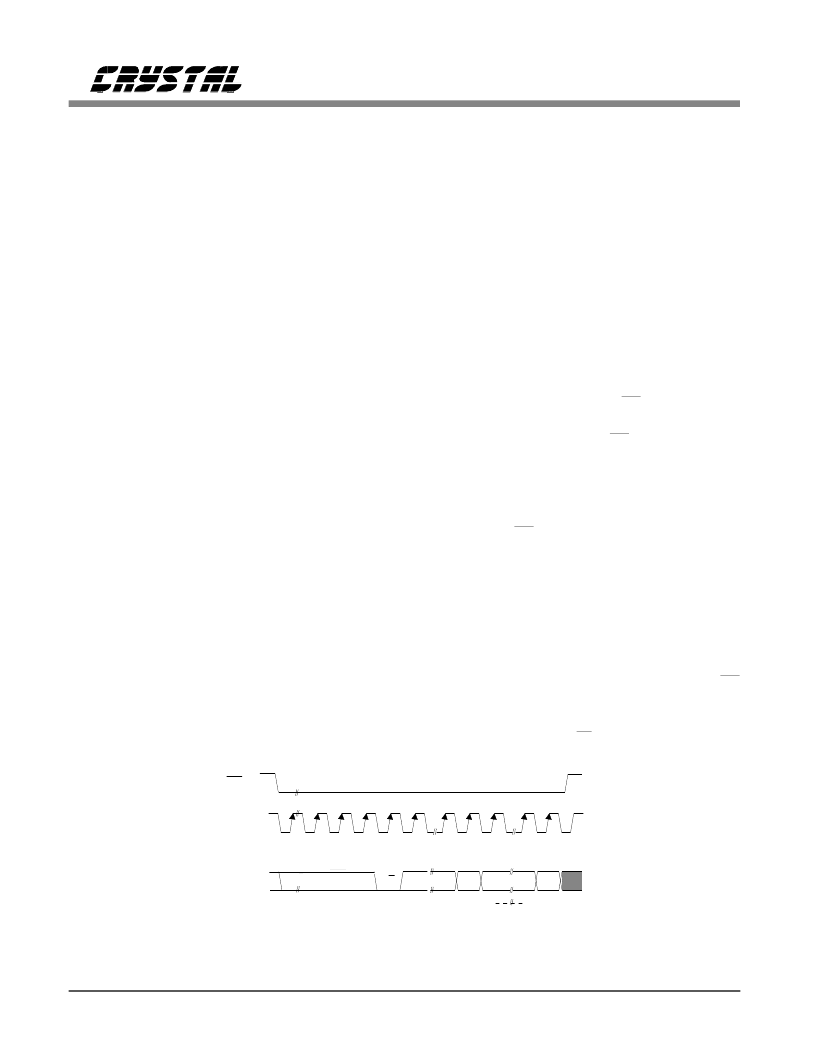

Figure 8 shows the operation of the control port

in SPI mode. To write to a register, bring CS

low. The first 7 bits on CDIN form the chip ad-

dress, and must be 0010000. The eighth bit is a

read/write indicator (R/W), which must be low

to write. Register reading from the CS4222 is

MAP

MSB

LSB

DATA

byte 1

byte n

R/W

MAP = Memory Address Pointer

ADDRESS

0010000

CHIP

CDIN

CCLK

CS

Figure 8. Control Port Timing, SPI mode

CS4222

14

DS236PP3

相关PDF资料 |

PDF描述 |

|---|---|

| CS4222 | 20-Bit Stereo Audio Codec with Volume Control |

| CS4224 | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-BS | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223 | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-KS | IC EEPROM SRL 1024X8BIT 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4223 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit 105 dB Audio Codec with Volume Control |

| CS4223_03 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-BS | 功能描述:接口—CODEC 24-Bit 105dB Ster Cod w/o Vol. Con. RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4223-DS | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-DSR | 功能描述:接口—CODEC 24-Bit 105dB Ster Cod w/o Vol. Con. RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。