- 您现在的位置:买卖IC网 > PDF目录380066 > CS4222-KS (CIRRUS LOGIC INC) 20-Bit Stereo Audio Codec with Volume Control PDF资料下载

参数资料

| 型号: | CS4222-KS |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 消费家电 |

| 英文描述: | 20-Bit Stereo Audio Codec with Volume Control |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封装: | SSOP-28 |

| 文件页数: | 16/26页 |

| 文件大小: | 580K |

| 代理商: | CS4222-KS |

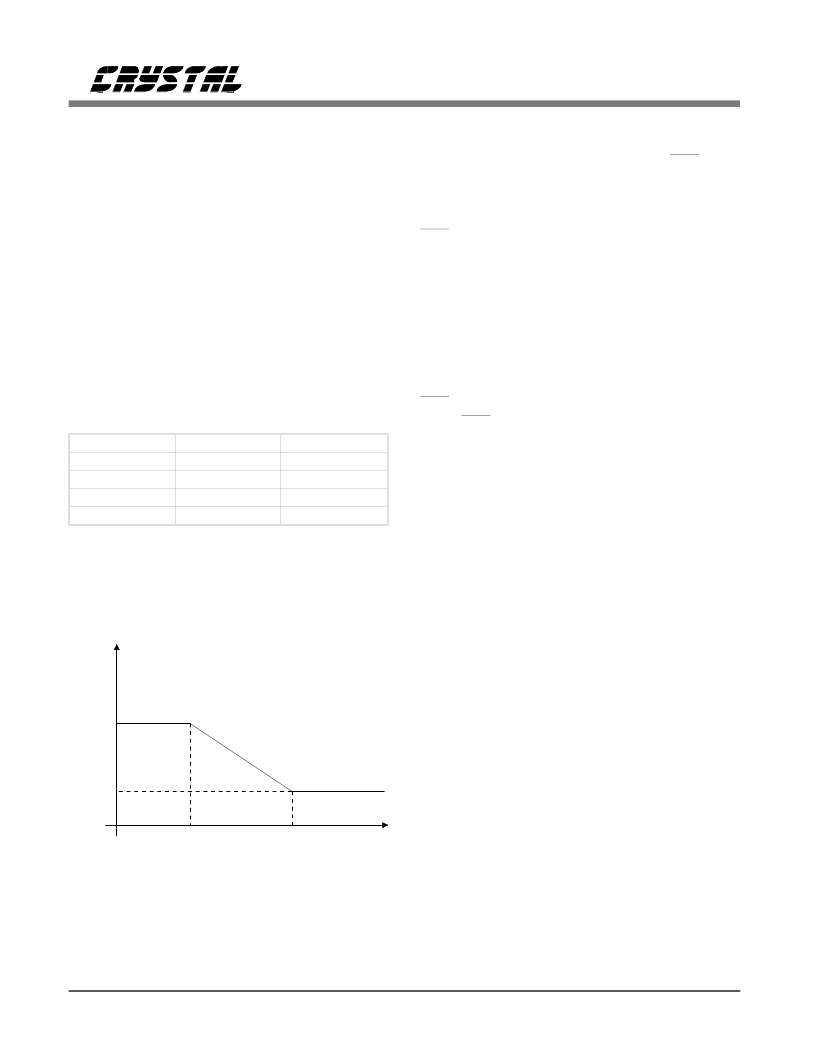

De-Emphasis

The CS4222 is capable of digital de-emphasis

for 32, 44.1, or 48 kHz sample rates. Imple-

mentation of digital de-emphasis requires

reconfiguration of the digital filter to maintain

the filter response shown in Figure 10 at multi-

ple sample rates.

De-emphasis control is achieved with the

DEM1/0 pins or through the DEM2-0 bits in the

DAC Control Byte (#2). The default state on

power-up is de-emphasis controlled via the

DEM1/0 pins (DEM2-0 bits=0). DEM1/0 pin

control is defined in Table 4.

DEM 1

0

0

1

1

DEM 0

0

1

0

1

De-emphasis

32 kHz

44.1 kHz

48 kHz

OFF

Table 4. De-Emphasis filter control

Power-up/Reset/Power Down/Calibration

Upon power up, the user should hold RST=0 for

approximately 10 ms. In this state, the control

port is reset to its default settings and the part

remains in the power down mode. At the end of

RST, the device performs an offset calibration

which lasts approximately 50 ms after which the

device enters normal operation. A calibration

may also be initiated via the CAL bit in the

ADC Control Byte (#1). The CALP bit in the

ADC Control Byte is a read only bit indicating

the status of the calibration.

Reset/Power Down is achieved by lowering the

RST pin causing the part to enter power down.

Once RST goes high, the control port is func-

tional and the desired settings should be loaded.

The CS4222 will also enter power down mode if

the master clock source stops for approximately

10

μ

s or if the LRCK is not synchronous to the

master clock. The control port will retain its

current settings.

Additionally, the PDAD (ADC Control Byte #1)

and PDDA (DAC Control Byte #2) bits can be

used to power down the ADC’s and DAC’s inde-

pendently. If both are set to 1, the CS4222 will

power down the entire chip. The control port

will retain its current settings.

The CS4222 will mute the analog outputs and

enter the power down mode if the supply drops

below approximately 4 volts.

Power Supply, Layout and Grounding

The CS4222 should be located on the analog

ground plane along with associated analog cir-

cuitry and should be positioned near the split

between ground planes (see Figure 11). Prefer-

ably, the device should also have its own power

plane. The +5V supply should be connected to

the CS4222 via a ferrite bead, positioned closer

than 1" to the device. A single connection be-

Gain

dB

-10dB

0dB

Frequency

T2 = 15

μ

s

T1=50

μ

s

F1

F2

Figure 10. De-emphasis Curve.

CS4222

16

DS236PP3

相关PDF资料 |

PDF描述 |

|---|---|

| CS4222 | 20-Bit Stereo Audio Codec with Volume Control |

| CS4224 | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-BS | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223 | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-KS | IC EEPROM SRL 1024X8BIT 8DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4223 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit 105 dB Audio Codec with Volume Control |

| CS4223_03 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-BS | 功能描述:接口—CODEC 24-Bit 105dB Ster Cod w/o Vol. Con. RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4223-DS | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-DSR | 功能描述:接口—CODEC 24-Bit 105dB Ster Cod w/o Vol. Con. RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。