- 您现在的位置:买卖IC网 > PDF目录380066 > CS4222 (Cirrus Logic, Inc.) 20-Bit Stereo Audio Codec with Volume Control PDF资料下载

参数资料

| 型号: | CS4222 |

| 厂商: | Cirrus Logic, Inc. |

| 元件分类: | Codec |

| 英文描述: | 20-Bit Stereo Audio Codec with Volume Control |

| 中文描述: | 20带有音量位立体声音频编解码器控制 |

| 文件页数: | 15/26页 |

| 文件大小: | 580K |

| 代理商: | CS4222 |

not supported in the SPI mode. The next 8 bits

form the Memory Address Pointer (MAP), which

is set to the address of the register that is to be

updated. The next 8 bits are the data which will

be placed into register designated by the MAP.

The CS4222 has a MAP auto increment capabil-

ity, enabled by the INCR bit in the MAP register.

If INCR is a zero, then the MAP will stay con-

stant for successive writes. If INCR is set to a 1,

then MAP will auto increment after each byte is

written, allowing block writes of successive reg-

isters. Register reading from the CS4222 is not

supported in the SPI mode.

I

2

C

Mode

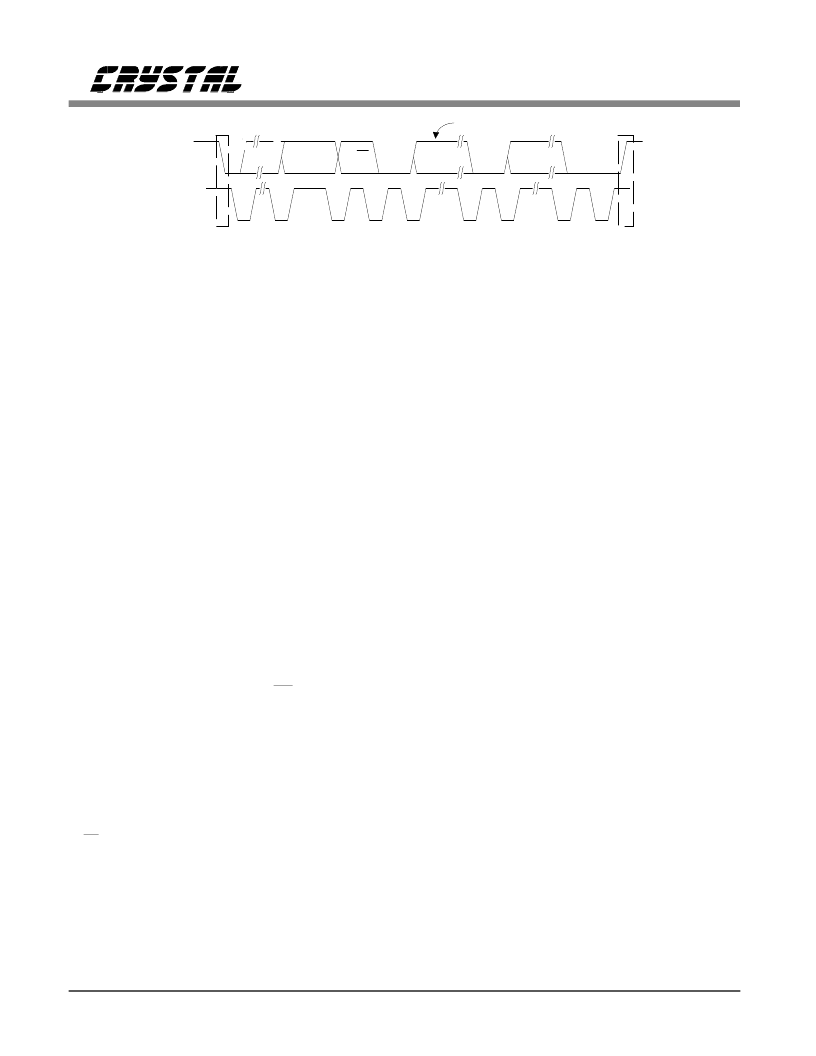

In I

2

C

mode, SDA is a bidirectional data line.

Data is clocked into and out of the part by the

clock, SCL, with the clock to data relationship as

shown in Figure 9. There is no CS pin. Pin AD0

forms the partial chip address and should be tied

to VD or DGND as desired. The upper 6 bits of

the 7 bit address field must be 001000. To com-

municate with the CS4222 the LSB of the chip

address field, which is the first byte sent to the

CS4222, should match the setting of the AD0

pin. The eighth bit of the address byte is the

R/W bit (high for a read, low for a write). If the

operation is a write, the next byte is the Memory

Address Pointer which selects the register to be

read or written. If the operation is a read, the

contents of the register pointed to by the Mem-

ory Address Pointer will be output. Setting the

auto increment bit in MAP, allows successive

reads or writes of consecutive registers. Each

byte is separated by an acknowledge bit. Use of

the I

2

C bus

compatible interface requires a li-

cense from Philips. I

2

C bus

is a registered

trademark of Philips Semiconductor.

Control Port Bit Definitions

All registers can be written and read in I

2

C

mode, except the Converter Status Report Byte

(#6) and the CLKE and CALP bits in the ADC

control byte (#1) which are read only. SPI mode

only allows for register writing. See the follow-

ing bit definition tables for bit assignment

information.

SDA

SCL

001000

ADDR

AD0

R/W

Start

ACK

DATA

1-8

ACK

DATA

1-8

ACK

Stop

Note: If operation is a write, this byte contains the Memory Address Pointer, MAP.

Figure 9. Control Port Timing, I

2

C

Mode

Note 1

CS4222

DS236PP3

15

相关PDF资料 |

PDF描述 |

|---|---|

| CS4224 | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-BS | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223 | 24-Bit 105 dB Audio Codec with Volume Control |

| CS4223-KS | IC EEPROM SRL 1024X8BIT 8DIP |

| CS4224-BS | 24-Bit 105 dB Audio Codec with Volume Control |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4222_02 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:20-Bit Stereo Audio Codec with Volume Control |

| CS4222-BS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS4222-DS | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cirrus Logic 功能描述: |

| CS4222-DSR | 功能描述:接口—CODEC 20-Bit Stereo Codec w/Vol. Cntrl. RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| CS4222-DSZ | 功能描述:接口—CODEC IC 20-Bit Stereo Codec w/Vol Cntrl RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。