参数资料

| 型号: | CS4384-CQZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 22/52页 |

| 文件大小: | 0K |

| 描述: | IC DAC 8CH 103DB 192KHZ 48-LQFP |

| 标准包装: | 2,000 |

| 位数: | 24 |

| 数据接口: | 串行 |

| 转换器数目: | 8 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 520mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 8 电压,单极 |

| 采样率(每秒): | 216k |

| 配用: | 598-1525-ND - BOARD EVAL FOR CS4384 DAC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

DS620F1

29

CS4384

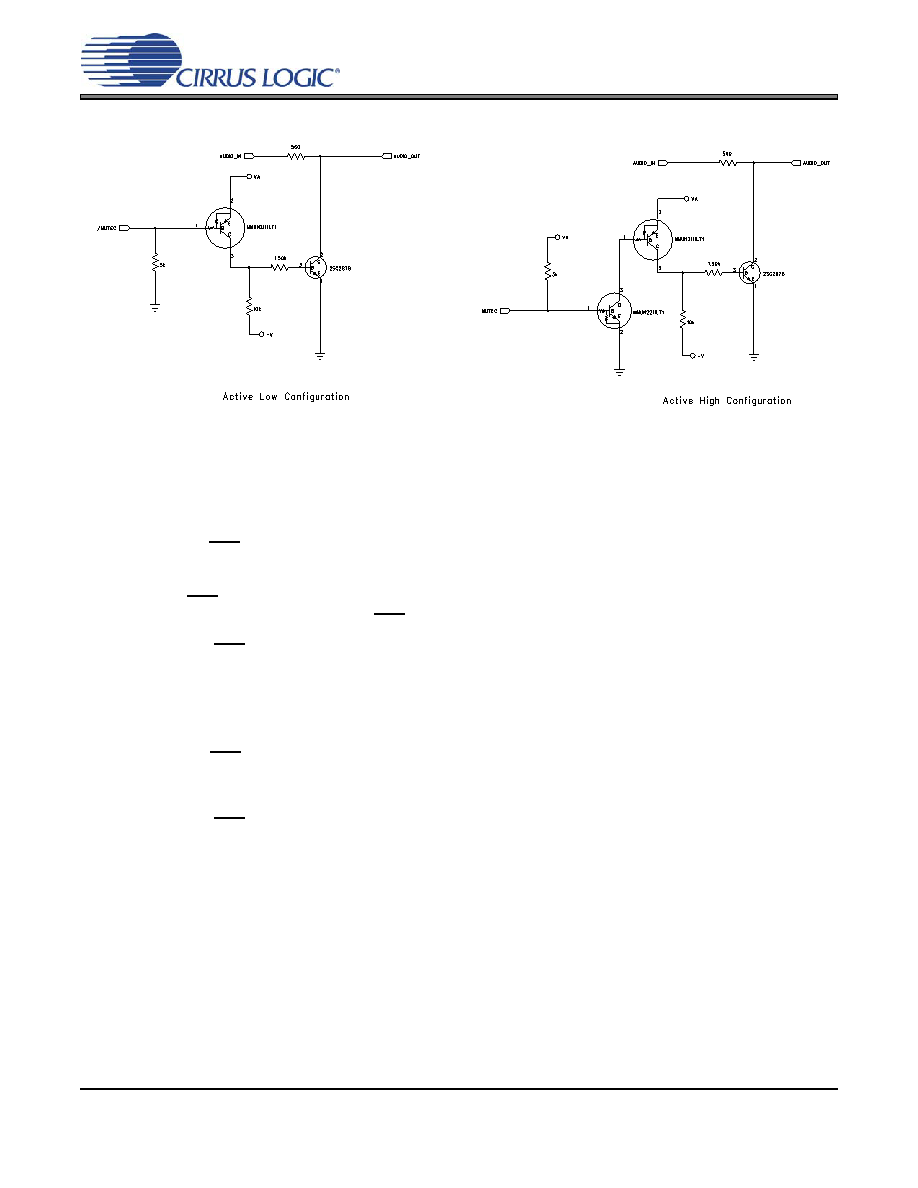

Figure 25. Recommended Mute Circuitry

4.12

Recommended Power-Up Sequence

4.12.1

Hardware Mode

1.

Hold RST low until the power supplies and configuration pins are stable, and the master and left/right

clocks are locked to the appropriate frequencies, as discussed in Section 4.1. In this state, the

registers are reset to the default settings, FILT+ will remain low, and VQ will be connected to VA/2.

If RST can not be held low long enough the SDINx pins should remain static low until all other clocks

are stable, and if possible the RST should be toggled low again once the system is stable.

2.

Bring RST high. The device will remain in a low power state with FILT+ low and will initiate the

Hardware power-up sequence after approximately 512 LRCK cycles in Single-Speed Mode (1024

LRCK cycles in Double-Speed Mode, and 2048 LRCK cycles in Quad-Speed Mode).

4.12.2

Software Mode

1.

Hold RST low until the power supply is stable, and the master and left/right clocks are locked to the

appropriate frequencies, as discussed in Section 4.1. In this state, the registers are reset to the default

settings, FILT+ will remain low, and VQ will be connected to VA/2.

2.

Bring RST high. The device will remain in a low power state with FILT+ low for 512 LRCK cycles in

Single-Speed Mode (1024 LRCK cycles in Double-Speed Mode, and 2048 LRCK cycles in Quad-

Speed Mode).

3.

In order to reduce the chances of clicks and pops, perform a write to the CP_EN bit prior to the

completion of approximately 512 LRCK cycles in Single-Speed Mode (1024 LRCK cycles in Double-

Speed Mode, and 2048 LRCK cycles in Quad-Speed Mode). The desired register settings can be

loaded while keeping the PDN bit set to 1. Set the RMP_UP and RMP_DN bits to 1, then set the

format and mode control bits to the desired settings.

If more than the stated number of LRCK cycles passes before CPEN bit is written then the chip will

enter Hardware Mode and begin to operate with the M0-M4 as the mode settings. CPEN bit may be

written at anytime, even after the Hardware sequence has begun. It is advised that if the CPEN bit

can not be set in time then the SDINx pins should remain static low (this way no audio data can be

相关PDF资料 |

PDF描述 |

|---|---|

| CS4385-DQZR | IC DAC 8CH 114DB 192KHZ 48-LQFP |

| CS4391A-KZZR | IC DAC 24BIT 192KHZ W/VC 20TSSOP |

| CS4392-KZZ | IC DAC 24BIT 192KHZ W/VC 20TSSOP |

| CS4397-KSZ | IC DAC 24BIT MULTY STNDRD 28SOIC |

| CS4398-CZZ | IC DAC 120DB 192KHZ W/VC 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS4384-DQZ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:103 dB, 192 kHz 8-Channel D/A Converter |

| CS4384-DQZR | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:103 dB, 192 kHz 8-Channel D/A Converter |

| CS4385 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192kHz 8-CHANNEL D/A CONVERTER |

| CS4385_07 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz 8-Channel D/A Converter |

| CS4385_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz 8-Channel D/A Converter |

发布紧急采购,3分钟左右您将得到回复。