- 您现在的位置:买卖IC网 > PDF目录26509 > CS495314-DVZ (CIRRUS LOGIC INC) PDF资料下载

参数资料

| 型号: | CS495314-DVZ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 颜色信号转换 |

| 中文描述: | COLOR SIGNAL DECODER, PQFP128 |

| 封装: | LEAD FREE, LQFP-128 |

| 文件页数: | 16/35页 |

| 文件大小: | 295K |

| 代理商: | CS495314-DVZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

CS4953xx Data Sheet

32-bit Audio Decoder DSP Family

DS705PP8

23

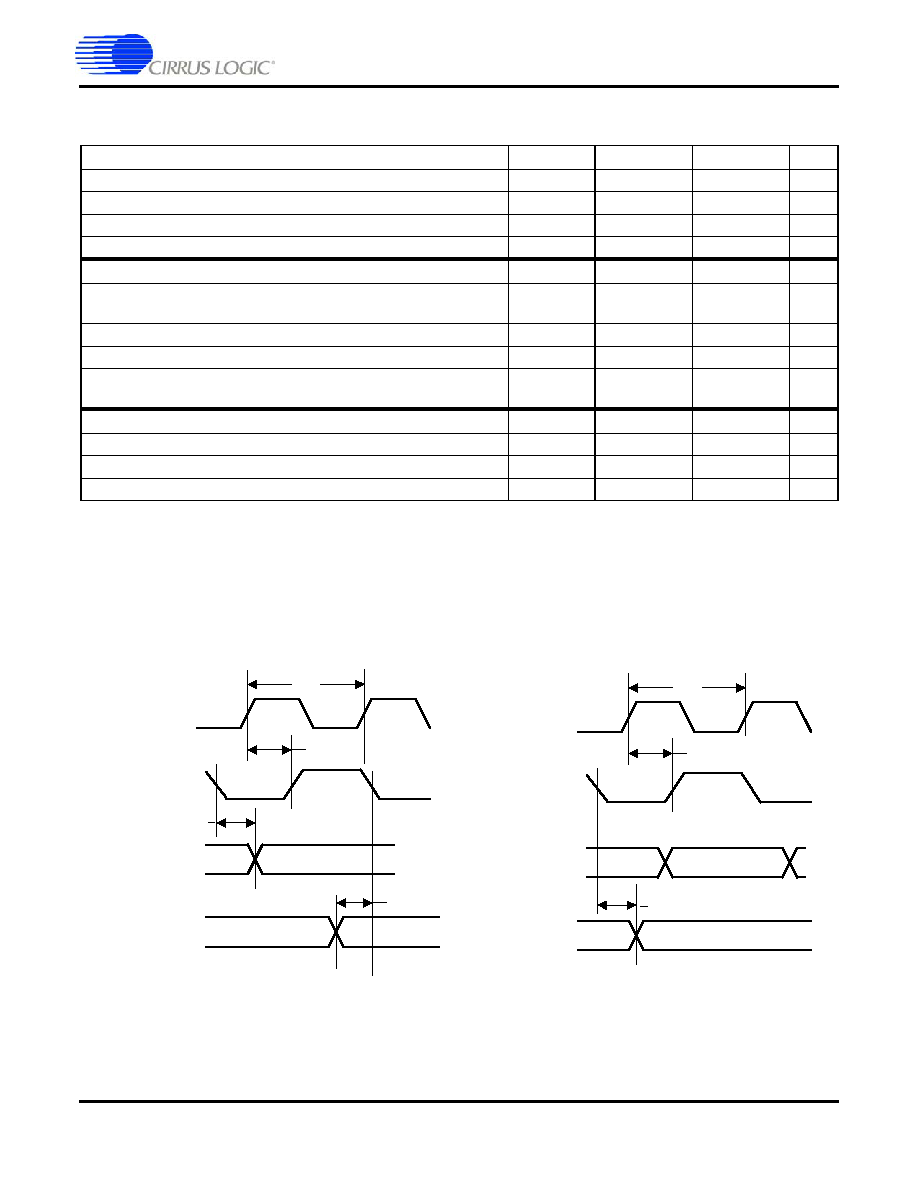

5.17 Switching Characteristics — Digital Audio Output Port

Figure 13. Digital Audio Port Output Timing Master Mode

Parameter

Symbol

Min

Max

Unit

DAO_MCLK period

Tdaomclk

40

—

ns

DAO_MCLK duty cycle

—45

55

%

DAO_SCLK period for Master or Slave mode1

1. Master mode timing specifications are characterized, not production tested.

Tdaosclk

40

—

ns

DAO_SCLK duty cycle for Master or Slave mode1

—40

60

%

Master Mode (Output A1 Mode)1,2

2. Master mode is defined as the CS4953xx driving both DAO_SCLK and DAO_LRCLK. When MCLK is an input, it is

divided to produce DAO_SCLK, DAO_LRCLK.

DAO_SCLK delay from DAO_MCLK rising edge,

DAO_MCLK as an input

tdaomsck

—19

ns

DAO_SCLK delay from DAO_LRCLK transition3

tdaomlrts

—8

ns

DAO_LRCLK delay from DAO_SCLK transition3

3. This timing parameter is defined from the non-active edge of DAO_SCLK. The active edge of DAO_SCLK is the

point at which the data is valid.

tdaomstlr

—8

ns

DAO1_DATA[3..0], DAO2_DATA[1..0]

delay from DAO_SCLK transition3

tdaomdv

—10

ns

Slave Mode (Output A0 Mode)4

4. Slave mode is defined as DAO_SCLK, DAO_LRCLK driven by an external source.

DAO_SCLK active edge to DAO_LRCLK transition

tdaosstlr

10

—

ns

DAO_LRCLK transition to DAO_SCLK active edge

tdaoslrts

10

—

ns

DAO_Dx delay from DAO_SCLK inactive edge

tdaosdv

—11

ns

DAO_MCLK

DAO_SCLK

DAO_LRCLK

DAOn_DATAn

tdaomlclk

tdaomsck

tdaomdv

tdaomlrts

DAO_MCLK

DAO_SCLK

DAO_LRCLK

DAOn_DATAn

tdaomclk

tdaomsck

tdaomstlr

Note: In these diagrams, Falling edge is the inactive edge of DAO_SCLK

相关PDF资料 |

PDF描述 |

|---|---|

| CS495314-DVZR | |

| CS495304-CVZ | |

| CS495304-CVZR | |

| CS5346-DQZR | |

| CS5346-DQZ | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS495314-DVZR | 功能描述:音频 DSP IC Multi-Channel Audio DSP Decoder RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| CS4953-CL | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:NTSC/PAL Digital Video Encoder |

| CS4953-CQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:NTSC/PAL Digital Video Encoder |

| CS4953XX | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit Audio Decoder DSP Family with Dual DSP Engine Technology |

| CS4953XX_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit Audio Decoder DSP Family |

发布紧急采购,3分钟左右您将得到回复。