- 您现在的位置:买卖IC网 > PDF目录26509 > CS495314-DVZ (CIRRUS LOGIC INC) PDF资料下载

参数资料

| 型号: | CS495314-DVZ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | 颜色信号转换 |

| 中文描述: | COLOR SIGNAL DECODER, PQFP128 |

| 封装: | LEAD FREE, LQFP-128 |

| 文件页数: | 5/35页 |

| 文件大小: | 295K |

| 代理商: | CS495314-DVZ |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

CS4953xx Data Sheet

32-bit Audio Decoder DSP Family

DS705PP8

13

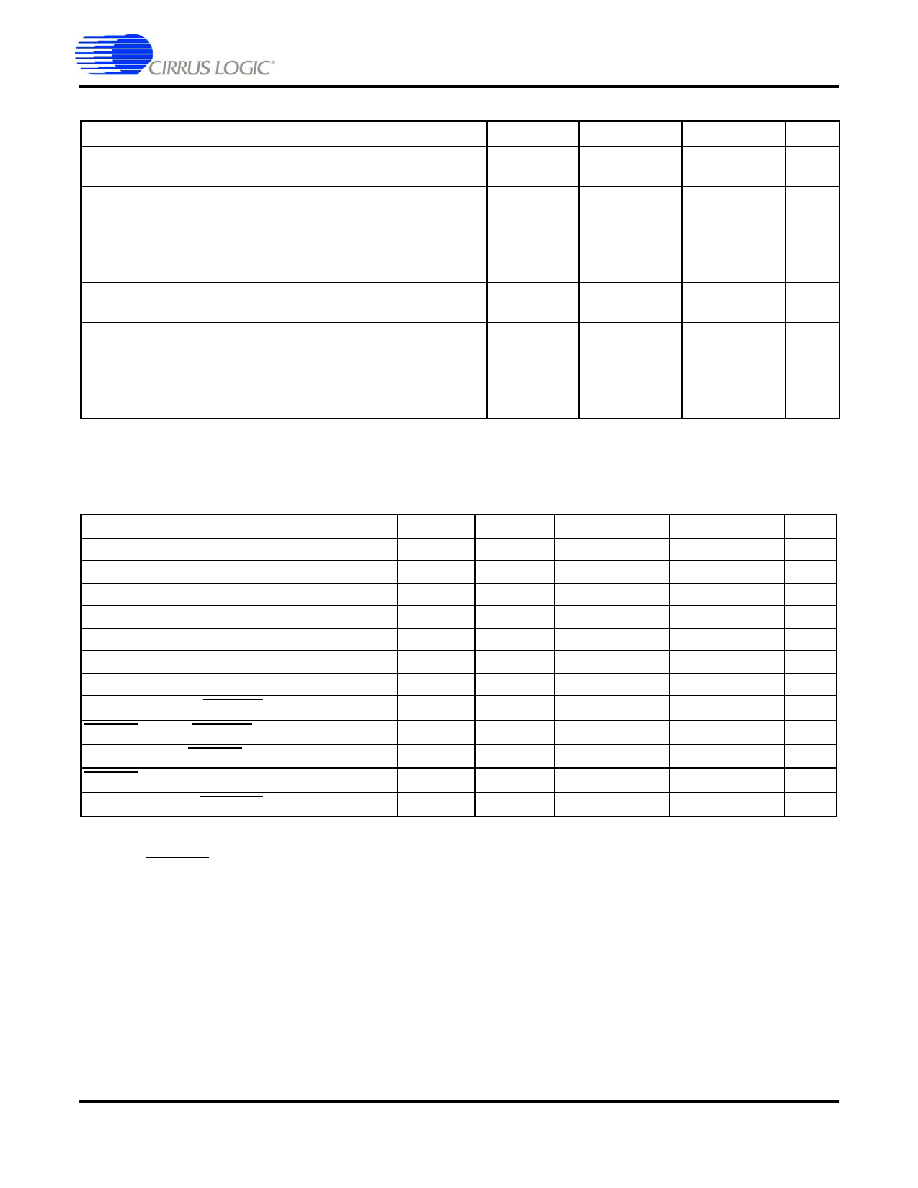

5.9 Switching Characteristics — Internal Clock

5.10 Switching Characteristics — Serial Control Port - SPI Slave Mode

Parameter

Symbol

Min

Max

Unit

Internal DCLK frequency1

1. After initial power-on reset, Fdclk = Fxtal. After initial kick-start commands, the PLL is locked to max Fdclk and remains

locked until the next power-on reset.

Fdclk

——

MHz

CS49530x-CVZ

CS49531x-CQZ

CS49531x-CVZ

CS49530x-DVZ

CS49531x-DVZ

—Fxtal

Fxtal

150

TBD

—

Internal DCLK period1

DCLKP

—

ns

CS49530x-CVZ

CS49531x-CQZ

CS49531x-CVZ

CS49530x-DVZ

CS49531x-DVZ

—6.7

6.7

TBD

1/Fxtal

—

Parameter

Symbol

Min

Typical

Max

Units

SCP_CLK frequency1

1. The specification fspisck indicates the maximum speed of the hardware. The system designer should be aware that

the actual maximum speed of the communication port may be limited by the firmware application. Flow control using

the SCP_BSY pin should be implemented to prevent overflow of the input data buffer. At boot the maximum speed

is Fxtal/3.

fspisck

——

25

MHz

SCP_CS falling to SCP_CLK rising

tspicss

24

—

ns

SCP_CLK low time

tspickl

20

—

ns

SCP_CLK high time

tspickh

20

—

ns

Setup time SCP_MOSI input

tspidsu

5—

—

ns

Hold time SCP_MOSI input

tspidh

5—

—

ns

SCP_CLK low to SCP_MISO output valid

tspidov

——

11

ns

SCP_CLK falling to SCP_IRQ rising

tspiirqh

—

20

ns

SCP_CS rising to SCP_IRQ falling

tspiirql

0—

—

ns

SCP_CLK low to SCP_CS rising

tspicsh

24

—

ns

SCP_CS rising to SCP_MISO output high-Z

tspicsdz

—20

—

ns

SCP_CLK rising to SCP_BSY falling

tspicbsyl

—3*DCLKP+20

—

ns

相关PDF资料 |

PDF描述 |

|---|---|

| CS495314-DVZR | |

| CS495304-CVZ | |

| CS495304-CVZR | |

| CS5346-DQZR | |

| CS5346-DQZ | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS495314-DVZR | 功能描述:音频 DSP IC Multi-Channel Audio DSP Decoder RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| CS4953-CL | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:NTSC/PAL Digital Video Encoder |

| CS4953-CQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:NTSC/PAL Digital Video Encoder |

| CS4953XX | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit Audio Decoder DSP Family with Dual DSP Engine Technology |

| CS4953XX_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:32-bit Audio Decoder DSP Family |

发布紧急采购,3分钟左右您将得到回复。