- 您现在的位置:买卖IC网 > PDF目录26510 > CS5346-DQZ (CIRRUS LOGIC INC) PDF资料下载

参数资料

| 型号: | CS5346-DQZ |

| 厂商: | CIRRUS LOGIC INC |

| 元件分类: | ADC |

| 中文描述: | 2-CH 24-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PQFP48 |

| 封装: | LEAD FREE, MS-022, LQFP-48 |

| 文件页数: | 15/40页 |

| 文件大小: | 402K |

| 代理商: | CS5346-DQZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

22

DS861PP2

CS5346

5.2.2

Master Mode

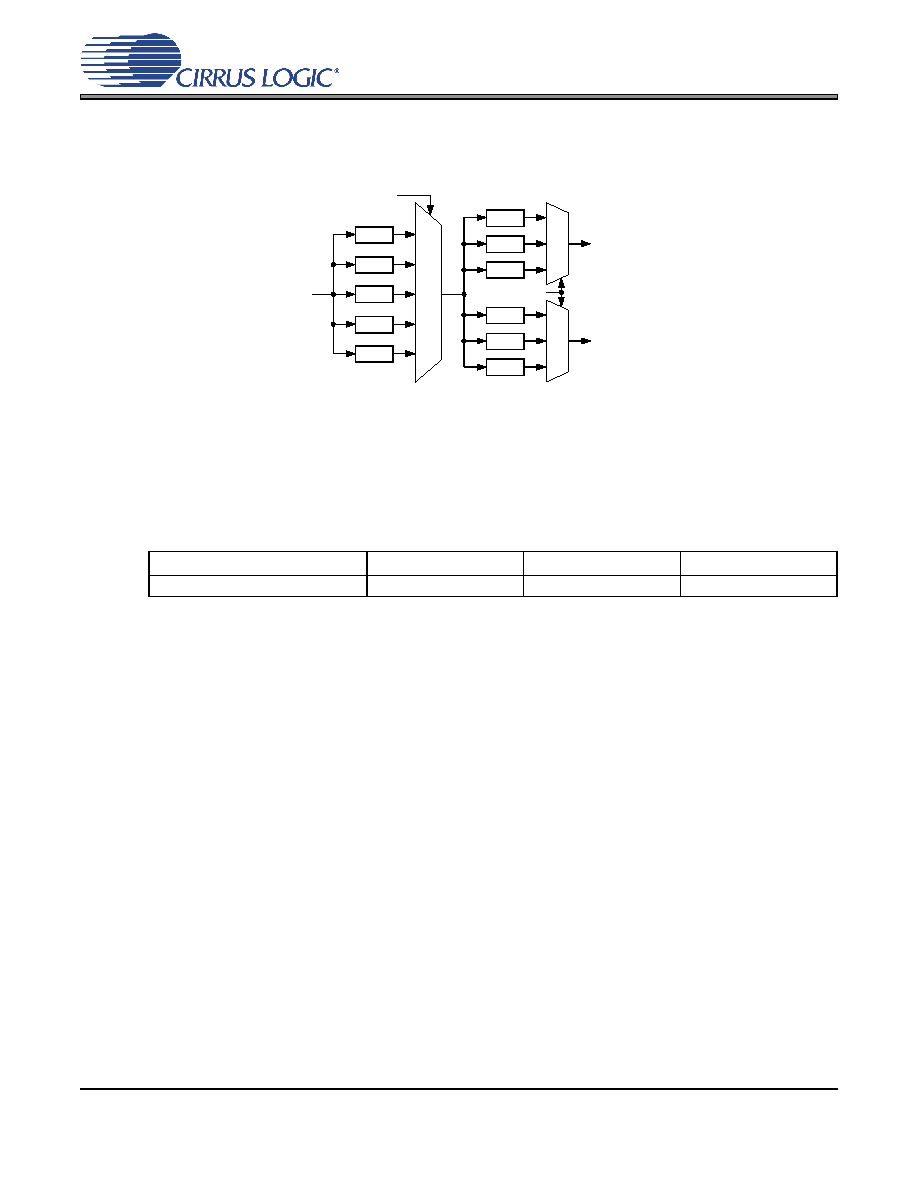

As a clock master, LRCK and SCLK will operate as outputs. LRCK and SCLK are internally derived from

MCLK with LRCK equal to Fs and SCLK equal to 64 x Fs as shown in Figure 8.

5.2.3

Slave Mode

In Slave Mode, SCLK and LRCK operate as inputs. The Left/Right clock signal must be equal to the sam-

ple rate, Fs, and must be synchronously derived from the supplied master clock, MCLK.

The serial bit clock, SCLK, must be synchronously derived from the master clock, MCLK, and be equal to

128x, 64x or 48x Fs, depending on the desired speed mode. Refer to Table 3 for required clock ratios.

5.3

High-Pass Filter and DC Offset Calibration

When using operational amplifiers in the input circuitry driving the CS5346, a small DC offset may be driven

into the A/D converter. The CS5346 includes a high-pass filter after the decimator to remove any DC offset

which could result in recording a DC level, possibly yielding clicks when switching between devices in a mul-

tichannel system.

The high-pass filter continuously subtracts a measure of the DC offset from the output of the decimation

filter. If the HPFFreeze bit (See “High-Pass Filter Freeze (Bit 1)” on page 31.) is set during normal operation,

the current value of the DC offset for the each channel is frozen and this DC offset will continue to be sub-

tracted from the conversion result. This feature makes it possible to perform a system DC offset calibration

by:

1. Running the CS5346 with the high-pass filter enabled until the filter settles. See the Digital Filter Char-

acteristics section for filter settling time.

2. Disabling the high-pass filter and freezing the stored DC offset.

A system calibration performed in this way will eliminate offsets anywhere in the signal path between the

calibration point and the CS5346.

Single-Speed

Double-Speed

Quad-Speed

SCLK/LRCK Ratio

48x, 64x, 128x

48x, 64x

Table 3. Slave Mode Serial Bit Clock Ratios

÷256

÷128

÷64

÷4

÷2

÷1

00

01

10

00

01

10

LRCK

SCLK

000

001

010

÷1

÷1.5

÷2

011

100

÷3

÷4

MCLK

FM Bits

MCLK Freq Bits

Figure 8. Master Mode Clocking

相关PDF资料 |

PDF描述 |

|---|---|

| CSBLA455KJ58-B0 | |

| CSTCC2M00G56-R0 | |

| CSTCE10M0G52A-R0 | |

| CSTCC2M00G56Z-R0 | |

| CSTCC5M00G53-R0 | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5346-DQZR | 功能描述:音频数/模转换器 IC 103dB 24Bit 192kHz Stereo Audio ADC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel |

| CS5349-000 | 制造商:TE Connectivity 功能描述:4110-10-340812 |

| CS5349-BP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit |

| CS5349-BS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit |

| CS5349-KP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 16-Bit |

发布紧急采购,3分钟左右您将得到回复。