- 您现在的位置:买卖IC网 > PDF目录20625 > CS5463-ISZR (Cirrus Logic Inc)IC ENERGY METERING 1PHASE 24SSOP PDF资料下载

参数资料

| 型号: | CS5463-ISZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 16/46页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METERING 1PHASE 24SSOP |

| 标准包装: | 1,000 |

| 输入阻抗: | 30 千欧 |

| 测量误差: | 0.1% |

| 电压 - 高输入/输出: | 0.8V |

| 电压 - 低输入/输出: | 0.2V |

| 电流 - 电源: | 2.9mA |

| 电源电压: | 4.75 V ~ 5.25 V |

| 测量仪表类型: | 单相 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 带卷 (TR) |

| 配用: | 598-1553-ND - BOARD EVAL & SOFTWARE CS5463 ADC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

�� �

�

�

�CS5463�

�5.� FUNCTIONAL� DESCRIPTION�

�250mV� P�

�---------------------� ?� 176.78mV�

�2�

�?� MCLK� ?� K� ?�

�5.1� Analog� Inputs�

�The� CS5463� is� equipped� with� two� fully� differential� input�

�channels.� The� inputs� VIN� ?� and� IIN� ?� are� designated� as�

�the� voltage� and� current� channel� inputs,� respectively.�

�The� full-scale� differential� input� voltage� for� the� current�

�and� voltage� channel� is� ?� 250� mV� P� .�

�5.1.1� Voltage� Channel�

�The� output� of� the� line� voltage� resistive� divider� or� trans-�

�former� is� connected� to� the� VIN+� and� VIN-� input� pins� of�

�the� CS5463.� The� voltage� channel� is� equipped� with� a�

�10x� fixed-gain� amplifier.� The� full-scale� signal� level� that�

�can� be� applied� to� the� voltage� channel� is� ?� 250� mV.� If� the�

�input� signal� is� a� sine� wave� the� maximum� RMS� voltage�

�at� a� gain� 10x� is:�

�RMS�

�which� is� approximately� 70.7%� of� maximum� peak� volt-�

�age.� The� voltage� channel� is� also� equipped� with� a� Volt-�

�age� Gain� Register� ,� allowing� for� an� additional�

�programmable� gain� of� up� to� 4x.�

�5.1.2� Current� Channel�

�The� output� of� the� current-sense� resistor� or� transformer�

�is� connected� to� the� IIN+� and� IIN-� input� pins� of� the�

�CS5463.� To� accommodate� different� current� sensing� el-�

�ements� the� current� channel� incorporates� a� programma-�

�ble� gain� amplifier� (PGA)� with� two� programmable� input�

�gains.� Configuration� Register� bit� Igain� (see� Table� 1)� de-�

�fines� the� two� gain� selections� and� corresponding� maxi-�

�mum� input-signal� level.�

�applied� to� the� voltage� and/or� current� channel,� the� maxi-�

�mum� input� range� should� be� adjusted� accordingly.�

�5.2� IIR� Filters�

�The� current� and� voltage� channel� are� equipped� with� a�

�4th-order� IIR� filter,� that� is� used� to� compensate� for� the�

�magnitude� roll� off� of� the� low-pass� decimation� filter.� Op-�

�erational� Mode� Register� bit� IIR� engages� the� IIR� filters� in�

�both� the� voltage� and� current� channels.�

�5.3� High-pass� Filters�

�By� removing� the� offset� from� either� channel,� no� error�

�component� will� be� generated� at� DC� when� computing� the�

�active� power.� By� removing� the� offset� from� both� chan-�

�nels,� no� error� component� will� be� generated� at� DC� when�

�computing� V� RMS� ,� I� RMS� ,� and� apparent� power.� Operation-�

�al� Mode� Register� bits� VHPF� and� IHPF� activate� the� HPF�

�in� the� voltage� and� current� channel� respectively.� When� a�

�high-pass� filter� is� active� in� only� one� channel,� an� all-pass�

�filter� (APF)� is� applied� to� the� other� channel.� The� APF� has�

�an� amplitude� response� that� is� flat� within� the� channel�

�bandwidth� and� is� used� for� matching� phase� in� systems�

�where� only� one� HPF� is� engaged.�

�5.4� Performing� Measurements�

�The� CS5463� performs� measurements� of� instantaneous�

�voltage� (V� n� )� and� current� (I� n� ),� and� calculates� instanta-�

�neous� power� (P� n� )� at� an� output� word� rate� (OWR)� of�

�OWR� =� -----------------------------�

�1024�

�where� K� is� the� clock� divider� selected� in� the� Configura-�

�tion� Register� .�

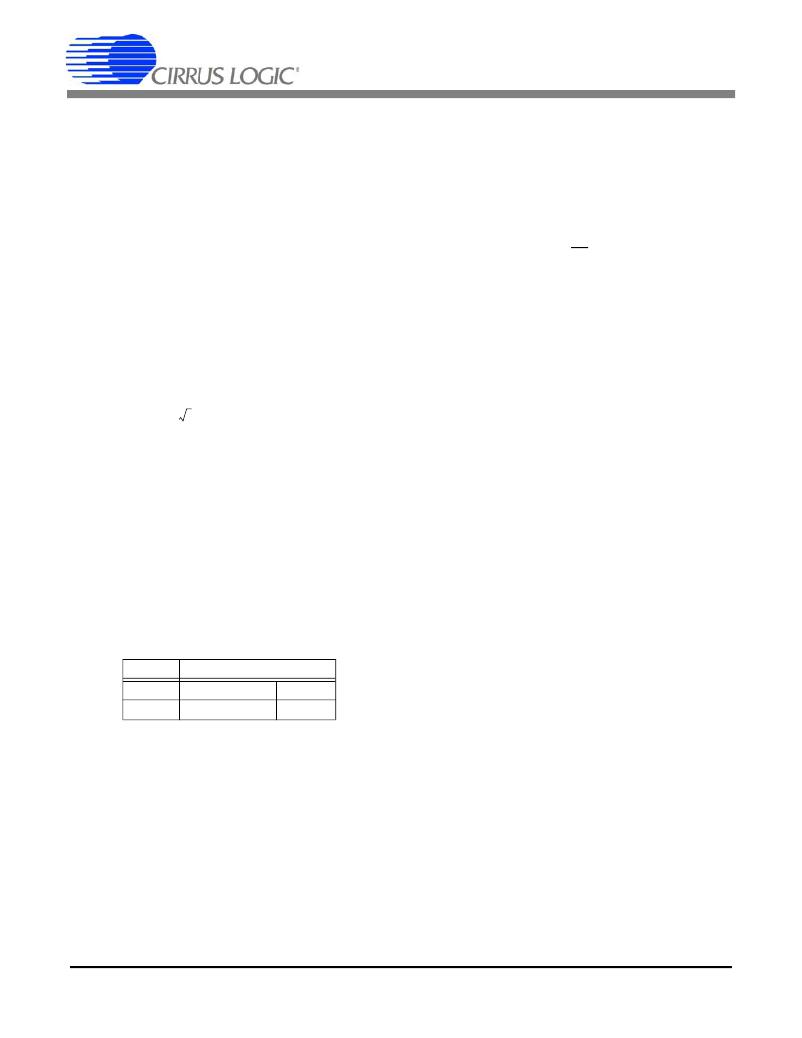

�Igain�

�Maximum� Input� Range�

�The� RMS� voltage� (V� RMS� ),� RMS� current� (I� RMS� ),� and� ac-�

�0�

�±250� mV�

�10x�

�tive� power� (P� active� )� are� computed� using� N� instantaneous�

�Computation� Cycle� =� ---------------�

�1� ±50� mV� 50x�

�Table� 1.� Current� Channel� PGA� Setting�

�For� example,� if� Igain=0,� the� current� channel’s� PGA� gain�

�is� set� to� 10x.� If� the� input� signals� are� pure� sinusoids� with�

�zero� phase� shift,� the� maximum� peak� differential� signal�

�on� the� current� or� voltage� channel� is� ?� 250� mV� P� .� The� in-�

�put� signal� levels� are� approximately� 70.7%� of� maximum�

�peak� voltage� producing� a� full-scale� energy� pulse� regis-�

�tration� equal� to� 50%� of� absolute� maximum� energy� pulse�

�registration.� This� will� be� discussed� further� in� See� Sec-�

�tion� 5.5� Energy� Pulse� Output� on� page� 17.�

�The� Current� Gain� Register� also� facilitates� an� additional�

�programmable� gain� of� up� to� 4x.� If� an� additional� gain� is�

�16�

�samples� of� V� n� ,� I� n� ,� and� P� n� respectively,� where� N� is� the�

�value� in� the� Cycle� Count� Register� and� is� referred� to� as�

�a� “� computation� cycle� ”.� The� apparent� power� (S)� is� the�

�product� of� V� RMS� and� I� RMS� .� A� computation� cycle� is� de-�

�rived� from� the� master� clock� (MCLK),� with� frequency:�

�OWR�

�N�

�Under� default� conditions� and� with� K� =� 1,� N� =� 4000,� and�

�MCLK� =� 4.096� MHz� –� the� OWR� =� 4000� Hz� and� the�

�Computation� Cycle� =� 1� Hz.�

�All� measurements� are� available� as� a� percentage� of� full�

�scale.� The� format� for� signed� registers� is� a� two’s� comple-�

�ment,� normalized� value� between� -1� and� +1.� The� format�

�DS678F3�

�相关PDF资料 |

PDF描述 |

|---|---|

| 591D227X9010R2T20H | CAP TANT 220UF 10V 10% 2824 |

| VI-BN4-EU-F1 | CONVERTER MOD DC/DC 48V 200W |

| RCM06DTMI-S189 | CONN EDGECARD 12POS R/A .156 SLD |

| GBM22DRXH | CONN EDGECARD 44POS DIP .156 SLD |

| V48C12H75BG | CONVERTER MOD DC/DC 12V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5463-ISZR/E2 | 制造商:Cirrus Logic 功能描述: |

| CS5464 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464_07 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464_11 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464-IS | 功能描述:电流和电力监控器、调节器 3-Ch Single Phase Power/Energy IC RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。