- 您现在的位置:买卖IC网 > PDF目录20625 > CS5463-ISZR (Cirrus Logic Inc)IC ENERGY METERING 1PHASE 24SSOP PDF资料下载

参数资料

| 型号: | CS5463-ISZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 21/46页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METERING 1PHASE 24SSOP |

| 标准包装: | 1,000 |

| 输入阻抗: | 30 千欧 |

| 测量误差: | 0.1% |

| 电压 - 高输入/输出: | 0.8V |

| 电压 - 低输入/输出: | 0.2V |

| 电流 - 电源: | 2.9mA |

| 电源电压: | 4.75 V ~ 5.25 V |

| 测量仪表类型: | 单相 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 带卷 (TR) |

| 配用: | 598-1553-ND - BOARD EVAL & SOFTWARE CS5463 ADC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

�� �

�

�

�CS5463�

�drive� the� device� from� an� external� clock� source,� XOUT�

�should� be� left� unconnected� while� XIN� is� driven� by� the�

�external� circuitry.� There� is� an� amplifier� between� XIN� and�

�the� digital� section� which� provides� CMOS� level� signals.�

�This� amplifier� works� with� sinusoidal� inputs� so� there� are�

�no� problems� with� slow� edge� times.�

�The� CS5463� can� be� driven� by� an� external� oscillator�

�ranging� from� 2.5� to� 20� MHz,� but� the� K� divider� value� must�

�be� set� such� that� the� internal� MCLK� will� run� somewhere�

�between� 2.5� MHz� and� 5� MHz.� The� K� divider� value� is� set�

�with� the� K[3:0]� bits� in� the� Configuration� Register� .� As� an�

�example,� if� XIN� =� MCLK� =� 15� MHz,� and� K� is� set� to� 5,�

�DCLK� will� equal� 3� MHz,� which� is� a� valid� value� for� DCLK.�

�5.13� Event� Handler�

�The� INT� pin� is� used� to� indicate� that� an� internal� error� or�

�event� has� taken� place� in� the� CS5463.� Writing� a� logic� 1�

�to� any� bit� in� the� Mask� Register� allows� the� corresponding�

�bit� in� the� Status� Register� to� activate� the� INT� pin.� The� in-�

�terrupt� condition� is� cleared� by� writing� a� logic� 1� to� the� bit�

�that� has� been� set� in� the� Status� Register� .�

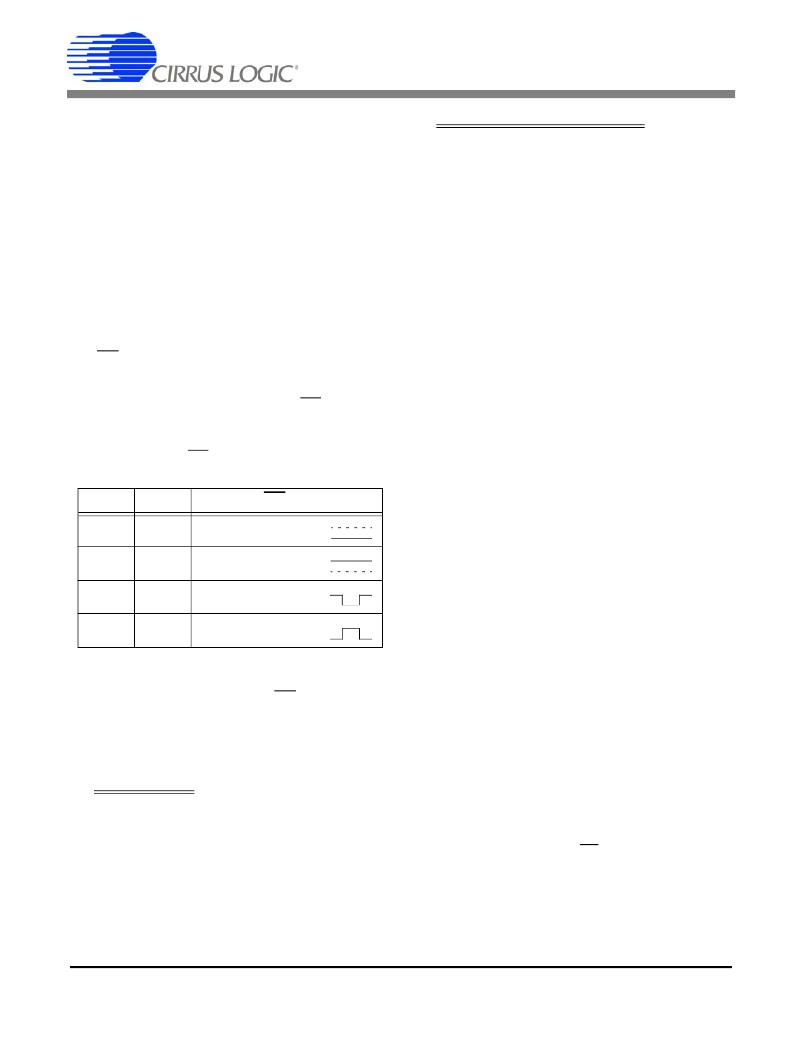

�The� behavior� of� the� INT� pin� is� controlled� by� the� IMODE�

�and� IINV� bits� of� the� Configuration� Register� .�

�INTERRUPT HANDLER ROUTINE� :�

�4)� Read� the� Status� Register.�

�5)� Disable� all� interrupts.�

�6)� Branch� to� the� proper� interrupt� service� routine.�

�7)� Clear� the� Status� Register� by� writing� back� the� read�

�value� in� step� 4.�

�8)� Re-enable� interrupt�

�9)� Return� from� interrupt� service� routine.�

�This� handshaking� procedure� ensures� that� any� new� in-�

�terrupts� activated� between� steps� 4� and� 7� are� not� lost�

�(cleared)� by� step� 7.�

�5.14� Serial� Port� Overview�

�The� CS5463� incorporates� a� serial� port� transmit� and� re-�

�ceive� buffer� with� a� command� decoder� that� interprets�

�one-byte� (8-bit)� commands� as� they� are� received.� There�

�are� four� types� of� commands:� instructions,� synchroniz-�

�ing,� register� writes,� and� register� reads� (See� Section�

�5.16� Commands� on� page� 23).�

�Instructions� are� one� byte� in� length� and� will� interrupt� any�

�instruction� currently� executing.� Instructions� do� not� affect�

�IMODE�

�0�

�IINV�

�0�

�INT� Pin�

�Active-low� Level�

�register� reads� currently� being� transmitted.�

�Synchronizing� commands� are� one� byte� in� length� and�

�only� affect� the� serial� interface.� Synchronizing� com-�

�mands� do� not� affect� operations� currently� in� progress.�

�0�

�1�

�Active-high� Level�

�Register� writes� must� be� followed� by� three� bytes� of� data.�

�Register� reads� can� return� up� to� four� bytes� of� data.�

�1�

�1�

�0�

�1�

�Low� Pulse�

�High� Pulse�

�Commands� and� data� are� transferred� most-significant� bit�

�(MSB)� first.� Figure� 1� on� page� 12,� defines� the� serial� port�

�timing� and� required� sequence� necessary� for� writing� to�

�and� reading� from� the� serial� port� receive� and� transmit�

�Table� 4.� Interrupt� Configuration�

�If� the� interrupt� output� signal� format� is� set� for� either� falling�

�or� rising� edge,� the� duration� of� the� INT� pulse� will� be� at�

�least� one� DCLK� cycle� (DCLK� =� MCLK/K).�

�5.13.1� Typical� Interrupt� Handler�

�The� steps� below� show� how� interrupts� can� be� handled.�

�INITIALIZATION� :�

�1)� All� Status� bits� are� cleared� by� writing� 0xFFFFFF� to�

�the� Status� Register.�

�2)� The� condition� bits� which� will� be� used� to� generate�

�interrupts� are� then� set� to� logic� 1� in� the� Mask� Reg-�

�ister.�

�3)� Enable� interrupts.�

�DS678F3�

�buffer,� respectively.� While� reading� data� from� the� serial�

�port,� commands� and� data� can� be� written� simultaneous-�

�ly.� Starting� a� new� register� read� command� while� data� is�

�being� read� will� terminate� the� current� read� in� progress.�

�This� is� acceptable� if� the� remainder� of� the� current� read�

�data� is� not� needed.� During� data� reads,� the� serial� port� re-�

�quires� input� data.� If� a� new� command� and� data� is� not�

�sent,� SYNC0� or� SYNC1� must� be� sent.�

�5.14.1� Serial� Port� Interface�

�The� serial� port� interface� is� a� “4-wire”� synchronous� serial�

�communications� interface.� The� interface� is� enabled� to�

�start� excepting� SCLKs� when� CS� (Chip� Select)� is� assert-�

�ed� (logic� 0).� SCLK� (Serial� bit-clock)� is� a� Schmitt-trigger�

�input� that� is� used� to� strobe� the� data� on� SDI� (Serial� Data�

�In)� into� the� receive� buffer� and� out� of� the� transmit� buffer�

�onto� SDO� (Serial� Data� Out).�

�21�

�相关PDF资料 |

PDF描述 |

|---|---|

| 591D227X9010R2T20H | CAP TANT 220UF 10V 10% 2824 |

| VI-BN4-EU-F1 | CONVERTER MOD DC/DC 48V 200W |

| RCM06DTMI-S189 | CONN EDGECARD 12POS R/A .156 SLD |

| GBM22DRXH | CONN EDGECARD 44POS DIP .156 SLD |

| V48C12H75BG | CONVERTER MOD DC/DC 12V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5463-ISZR/E2 | 制造商:Cirrus Logic 功能描述: |

| CS5464 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464_07 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464_11 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Three-channel, Single-phase Power/Energy IC |

| CS5464-IS | 功能描述:电流和电力监控器、调节器 3-Ch Single Phase Power/Energy IC RoHS:否 制造商:STMicroelectronics 产品:Current Regulators 电源电压-最大:48 V 电源电压-最小:5.5 V 工作温度范围:- 40 C to + 150 C 安装风格:SMD/SMT 封装 / 箱体:HPSO-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。