参数资料

| 型号: | CS5529-ASZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 10/31页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT W/6BIT LATCH 20SSOP |

| 标准包装: | 1,000 |

| 位数: | 16 |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 3.5mW |

| 电压电源: | 双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个差分,单极;1 个差分,双极 |

| 配用: | 598-1015-ND - EVAL BOARD FOR CS5529 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

CS5529

18

DS246F5

Gain Register

The gain register span is from 0 to (4-2-22). After Reset the (MSB-1) bit is ‘1’, all other bits are ‘0’.

The gain calibration results is stored in the gain

register. The result sets the slope of the ADC’s

transfer function. The gain register spans from 0 to

(4 - 2-22). The decimal equivalent meaning of the

gain register is

where the binary numbers have a value of either

zero or one (b0 corresponds to bit MSB-1, N = 22).

Self Calibration

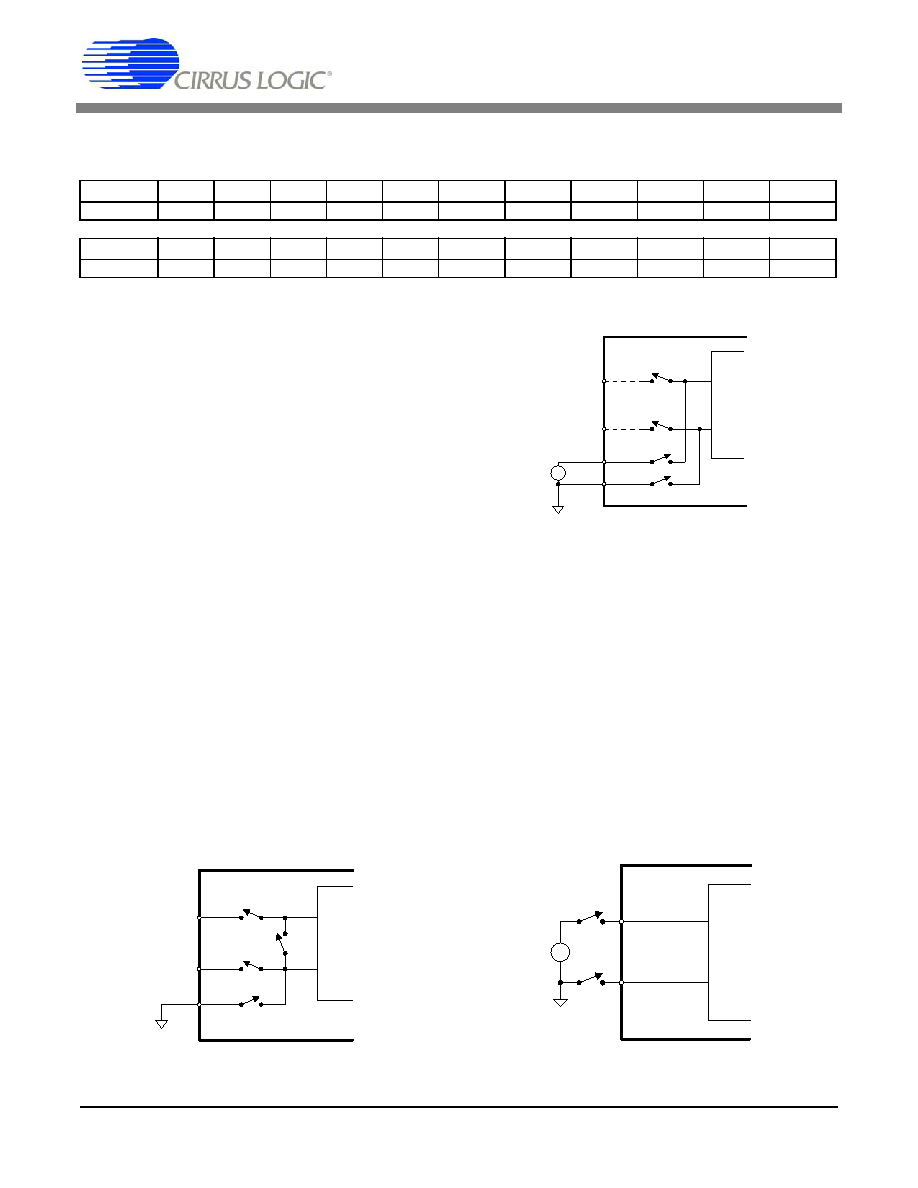

The CS5529 offers both self offset and self gain

calibrations. For the self-calibration of offset, the

converter internally ties the inputs of the modulator

together and routes them to the VREF- pin as

shown in Figure 6. Also self offset calibration re-

quires that VREF- be tied to a fixed voltage be-

tween VA+ and VA-. For self-calibration of gain,

the differential inputs of the modulator are connect-

ed to VREF+ and VREF- as shown in Figure7.

System Calibration

For the system calibration functions, the user must

input signals which represent system ground and

system full scale to the converter. When a system

offset calibration is performed a ground reference

signal must be applied to the converter (see Figure

8). When a system gain calibration is performed,

the user must input a signal representing the posi-

tive full scale point as shown in Figure 9. In either

case, calibration signals must be within the speci-

fied calibration limits for each specific calibration

step (refer to the System Calibration Specifica-

23(MSB)

22

21

20

19

18

17

16

15

14

13

12

21

20

2-1

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

2-10

0

00000

0

11

10

9876

5

4

3

2

1

0

2-11

2-12

2-13

2-14

2-15

2-16

2-17

2-18

2-19

2-20

2-21

2-22

0

00000

0

Db

MSB

2

1

b

(

0

2

0

b

1

2

1

–

… b

N

2

N

– )

++

+

b

MSB

2

1

b

i

2

i

–

i

0

=

N

∑

+

==

AIN+

AIN-

S1

OPEN

+

-

S2

OPEN

S4

CLOSED

VREF-

S3

CL

O

SED

Figure 6. Self Calibration of Offset.

AIN+

AIN-

OPEN

+

-

OPEN

CLOSED

VREF+

CLOSED

VREF-

+

-

Reference

Figure 7. Self Calibration of Gain.

+

-

External

Connections

0V +

-

AIN+

AIN-

Figure 8. System Calibration of Offset.

相关PDF资料 |

PDF描述 |

|---|---|

| CS5530-ISZR | IC ADC 24BIT 1CH W/LNA 20-SSOP |

| CS5534-ASZR | IC ADC 24BIT 4CH W/LNA 24-SSOP |

| CS5534-BSZR | IC ADC 24BIT 4CH W/LNA 24SSOP |

| CS5550-ISZR | IC ADC 2CH LOW-COST 24-SSOP |

| CS5565-ISZ | IC ADC DELTA-SIGMA 24BIT 24-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5530 | 制造商:Texas Instruments 功能描述: |

| CS5530_0911 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-bit ADC with Ultra-low-noise Amplifier |

| CS5530A | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:AMD Geode CS5530A Companion Device |

| CS5530A-UCE | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:AMD Geode CS5530A Companion Device |

| CS5530A-UCE B1 | 制造商:Advanced Micro Devices 功能描述:DICCX5530 |

发布紧急采购,3分钟左右您将得到回复。