- 您现在的位置:买卖IC网 > PDF目录10669 > CS5532-BSZ (Cirrus Logic Inc)IC ADC 24BIT 2CH W/LNA 20SSOP PDF资料下载

参数资料

| 型号: | CS5532-BSZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 30/43页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT 2CH W/LNA 20SSOP |

| 标准包装: | 66 |

| 位数: | 24 |

| 采样率(每秒): | 3.84k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 45mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个差分,单极;2 个差分,双极 |

| 产品目录页面: | 755 (CN2011-ZH PDF) |

| 配用: | 598-1159-ND - BOARD EVAL FOR CS5532U ADC |

| 其它名称: | 598-1113-5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

CS5531/32/33/34-AS

36

DS289F5

offset calibration on physical channel 2 and SDO

falls to indicate that the calibration is complete. To

perform additional calibrations, more commands

must be issued.

Note:

The CSRs need not be written. If they are not

initialized, all the Setups point to their default

settings irrespective of the conversion or

calibration mode (i.e conversions can be

performed, but only physical channel 1 will be

converted). Further note that filter

convolutions are reset (i.e. flushed) if

consecutive conversions are performed on

two different physical channels. If

consecutive conversions are performed on

the same physical channel, the filter is not

reset. This allows the ADCs to more quickly

settle full-scale step inputs.

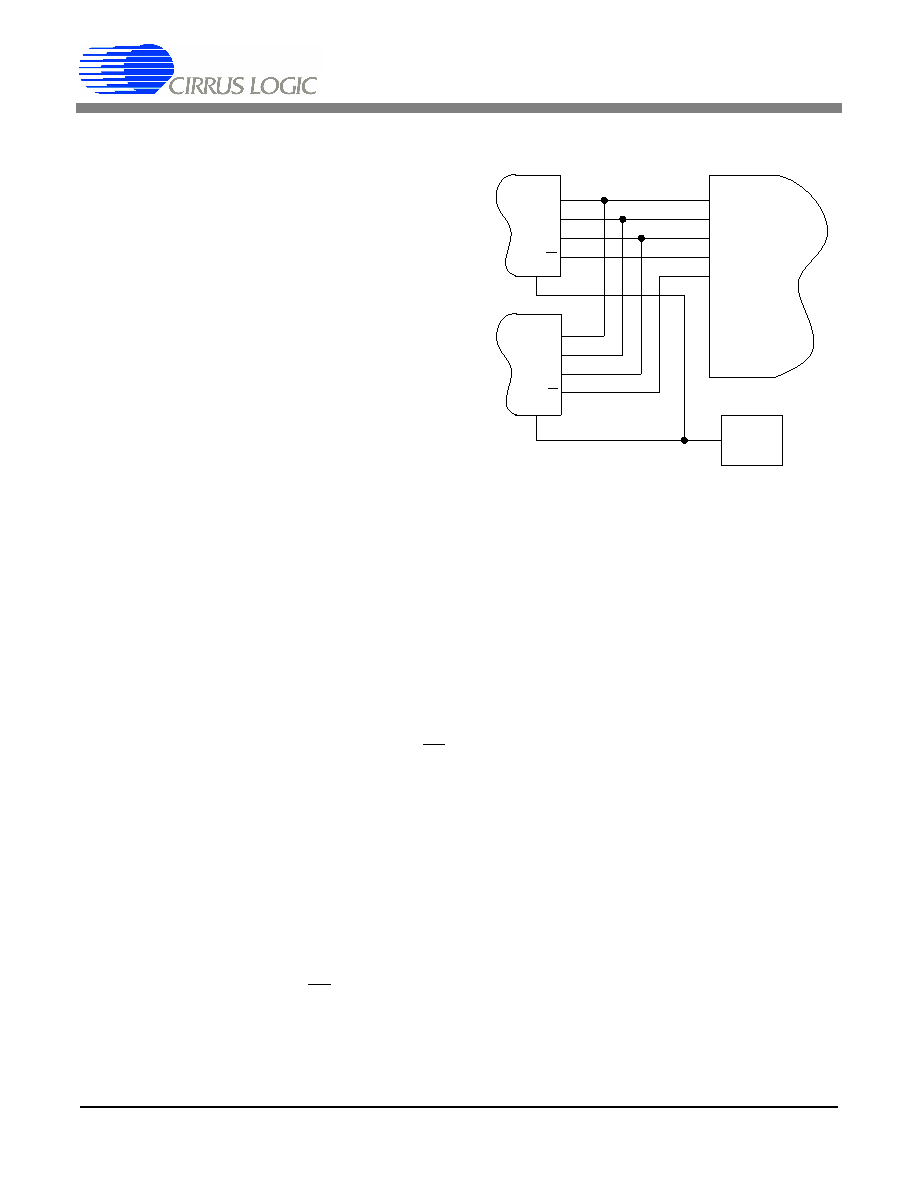

2.7. Using Multiple ADCs Synchronously

Some applications require synchronous data out-

puts from multiple ADCs converting different ana-

log channels. Multiple CS5531/32/33/34 parts can

be synchronized in a single system by using the fol-

lowing guidelines:

1) All of the ADCs in the system must be operated

from the same oscillator source.

2) All of the ADCs in the system must share com-

mon SCLK and SDI lines.

3) A software reset must be performed at the same

time for all of the ADCs after system power-up (by

selecting all of the ADCs using their respective CS

pins, and writing the reset sequence to all parts, us-

ing SDI and SCLK).

4) A start conversion command must be sent to all

of the ADCs in the system at the same time. The ±8

clock cycles of ambiguity for the first conversion

(or for a single conversion) will be the same for all

ADCs, provided that they were all reset at the same

time.

5) Conversions can be obtained by monitoring

SDO on only one ADC, (bring CS high for all but

one part) and reading the data out of each part indi-

vidually, before the next conversion data words are

ready.

An example of a synchronous system using two

CS5532 parts is shown in Figure 15.

2.8. Conversion Output Coding

The CS5531/33 output 16-bit data conversion

words and the CS5532/34 output 24-bit data con-

version words. To read a conversion word the user

must read the conversion data register. The conver-

sion data register is 32 bits long and outputs the

conversions MSB first. The last byte of the conver-

sion data register contains data monitoring flags.

The channel indicator (CI) bits keep track of which

physical channel was converted and the overrange

flag (OF) monitors to determine if a valid conver-

sion was performed. Refer to the Conversion Data

Output Descriptions section for more details.

The CS5531/32/33/34 output data conversions in

binary format when operating in unipolar mode and

in two's complement format when operating in bi-

for both unipolar and bipolar mode. VFS in the ta-

bles refers to the positive full-scale voltage range of

the converter in the specified gain range, and -VFS

refers to the negative full-scale voltage range of the

converter. The total differential input range (be-

tween AIN+ and AIN-) is from 0 to VFS in unipo-

lar mode, and from -VFS to VFS in bipolar mode.

CLOCK

SOURCE

CS5532

SDO

SDI

SCLK

CS

OSC2

SDO

SDI

SCLK

CS

OSC2

C

Figure 15. Synchronizing Multiple ADCs

相关PDF资料 |

PDF描述 |

|---|---|

| VI-2WZ-IV-B1 | CONVERTER MOD DC/DC 2V 60W |

| VE-26B-IX-B1 | CONVERTER MOD DC/DC 95V 75W |

| VI-2WT-IX-B1 | CONVERTER MOD DC/DC 6.5V 75W |

| VE-261-IX-B1 | CONVERTER MOD DC/DC 12V 75W |

| VI-2WL-IX-B1 | CONVERTER MOD DC/DC 28V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5532-BSZ/H | 制造商:Cirrus Logic 功能描述: |

| CS5532-BSZR | 功能描述:模数转换器 - ADC IC 16-Bit ADCs w/UltraLw Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5533 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-bit and 24-bit ADCs with Ultra-low-noise PGIA |

| CS5533-AS | 功能描述:模数转换器 - ADC 4-Ch 16-Bit ADCs w/ Ultra Low Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5533-ASR | 功能描述:模数转换器 - ADC IC 16-Bit ADCs w/UltraLw Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。