- 您现在的位置:买卖IC网 > PDF目录10250 > CS5532-BSZR (Cirrus Logic Inc)IC ADC 24BIT 2CH W/LNA 20-SSOP PDF资料下载

参数资料

| 型号: | CS5532-BSZR |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 15/17页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT 2CH W/LNA 20-SSOP |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 3.84k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 45mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个差分,单极;2 个差分,双极 |

| 配用: | 598-1159-ND - BOARD EVAL FOR CS5532U ADC |

IDT / ICS PCI EXPRESS JITTER ATTENUATOR

7

ICS9DB202CK-01 REV. B FEBRUARY 18, 2009

ICS9DB202-01

PCI EXPRESS JITTER ATTENUATOR

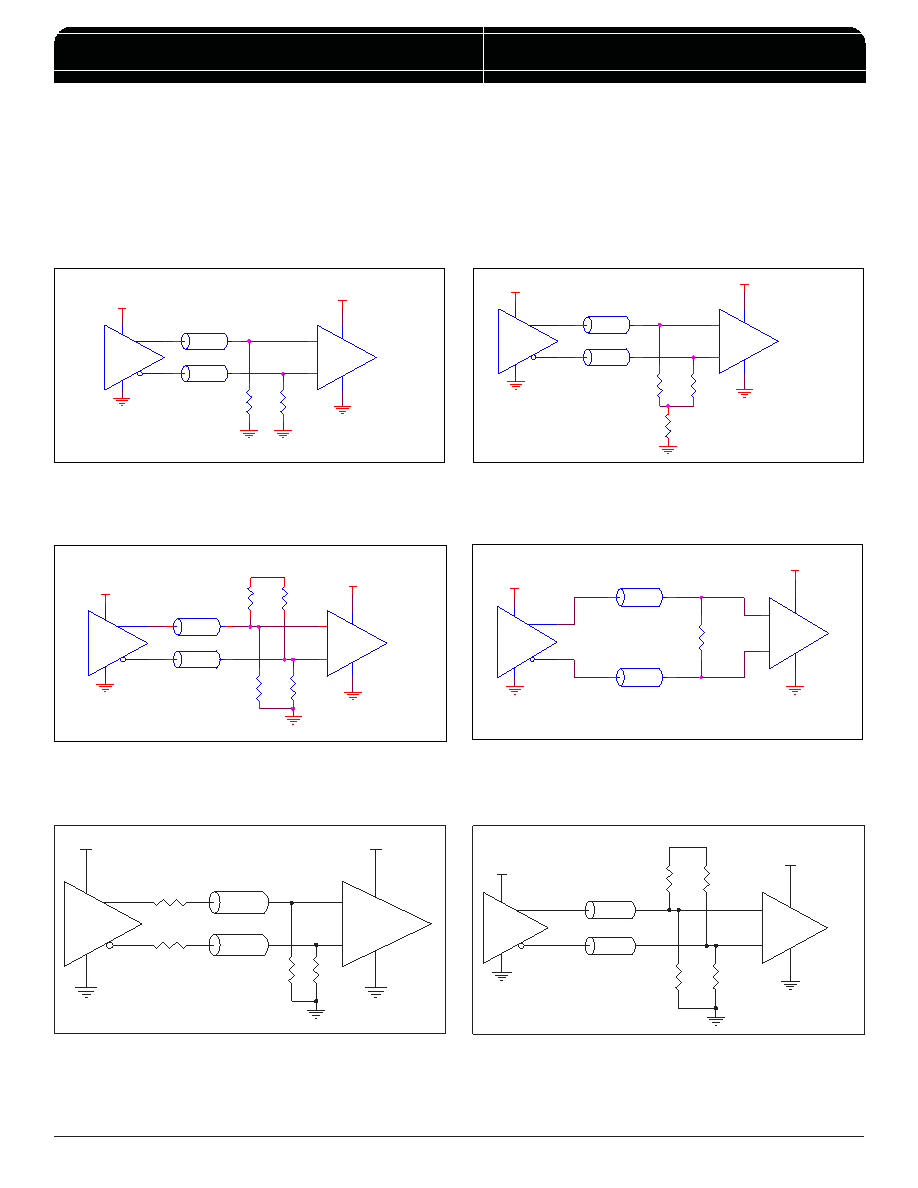

FIGURE 3C. HIPERCLOCKS CLK/nCLK INPUT

DRIVEN BY A 3.3V LVPECL DRIVER

FIGURE 3B. HIPERCLOCKS CLK/nCLK INPUT

DRIVEN BY A 3.3V LVPECL DRIVER

FIGURE 3D. HIPERCLOCKS CLK/nCLK INPUT

DRIVEN BY A 3.3V LVDS DRIVER

3.3V

R1

50

R3

50

Zo = 50 Ohm

LVPECL

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

3.3V

Input

R2

50

Zo = 50 Ohm

Input

HiPerClockS

CLK

nCLK

3.3V

R3

125

R2

84

Zo = 50 Ohm

3.3V

R4

125

LVPECL

R1

84

3.3V

DIFFERENTIAL CLOCK INPUT INTERFACE

The CLK /nCLK accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL

and other differential signals. Both signals must meet the V

PP

and V

CMR input

requirements. Figures

4A to 4F show interface

examples for the HiPerClockS CLK/nCLK input driven by the

most common driver types. The input interfaces suggested here

are examples only. Please consult with the vendor of the driver

FIGURE 3A. HIPERCLOCKS CLK/nCLK INPUT

DRIVEN BY AN IDT OPEN EMITTER

HIPERCLOCKS LVHSTL DRIVER

component to confirm the driver termination requirements. For

example in Figure 4A, the input termination applies for IDT

HiPerClockS open emitter LVHSTL drivers. If you are using an

LVHSTL driver from another vendor, use their termination

recommendation.

1.8V

R2

50

Input

LVHSTL Driver

ICS

HiPerClockS

R1

50

LVHSTL

3.3V

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

FIGURE 3E. HIPERCLOCKS CLK/nCLK INPUT

DRIVEN BY A 3.3V HCSL DRIVER

Zo = 50 Ohm

R1

100

3.3V

LVDS_Driv er

Zo = 50 Ohm

Receiv er

CLK

nCLK

3.3V

HCSL

*R3

33

*R4

33

CLK

nCLK

2.5V

3.3V

Zo = 50

Ω

Zo = 50

Ω

HiPerClockS

Input

R1

50

R2

50

*Optional – R3 and R4 can be 0

Ω

FIGURE 3F.

HIPERCLOCKS CLK/nCLK INPUT

DRIVEN BY A 2.5V SSTL DRIVER

CLK

nCLK

HiPerClockS

SSTL

2.5V

Zo = 60

Ω

Zo = 60

Ω

2.5V

3.3V

R1

120

R2

120

R3

120

R4

120

相关PDF资料 |

PDF描述 |

|---|---|

| LTC1851IFW#PBF | IC ADC 12BIT 1.25MSPS 48-TSSOP |

| LTC1851IFW | IC ADC 12BIT 1.25MSPS 48-TSSOP |

| MS27467T11A35PB | CONN PLUG 13POS STRAIGHT W/PINS |

| LTC1853IFW#PBF | IC A/D CONV 8CH 12BIT 48-TSSOP |

| VE-232-IW-S | CONVERTER MOD DC/DC 15V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5533 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:16-bit and 24-bit ADCs with Ultra-low-noise PGIA |

| CS5533-AS | 功能描述:模数转换器 - ADC 4-Ch 16-Bit ADCs w/ Ultra Low Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5533-ASR | 功能描述:模数转换器 - ADC IC 16-Bit ADCs w/UltraLw Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5533-ASZ | 功能描述:模数转换器 - ADC 4-Ch 16-Bit ADCs w/ Ultra Low Noise PGIA RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| CS5533-ASZ/H1 | 制造商:Cirrus Logic 功能描述: |

发布紧急采购,3分钟左右您将得到回复。