- 您现在的位置:买卖IC网 > PDF目录223637 > CY2308SI-2 (CYPRESS SEMICONDUCTOR CORP) 3.3V Zero Delay Buffer PDF资料下载

参数资料

| 型号: | CY2308SI-2 |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | 时钟及定时 |

| 英文描述: | 3.3V Zero Delay Buffer |

| 中文描述: | 2308 SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, MS-012, SOIC-16 |

| 文件页数: | 1/17页 |

| 文件大小: | 503K |

| 代理商: | CY2308SI-2 |

CY2308

3.3 V Zero Delay Buffer

Cypress Semiconductor Corporation

198 Champion Court

San Jose

, CA 95134-1709

408-943-2600

Document Number: 38-07146 Rev. *L

Revised October 11, 2010

Features

■ Zero input-output propagation delay, adjustable by capacitive

load on FBK input

■ Multiple configurations, see Available CY2308 Configurations

on page 4 for more details

■ Multiple low skew outputs

■ Two banks of four outputs, three-stateable by two select inputs

■ 10 MHz to 133 MHz operating range

■ 75 ps typical cycle-to-cycle jitter (15 pF, 66 MHz)

■ Space saving 16-pin 150 mil SOIC package or 16-pin TSSOP

■ 3.3 V operation

■ Industrial temperature available

Functional Description

The CY2308 is a 3.3 V Zero Delay Buffer designed to distribute

high speed clocks in PC, workstation, datacom, telecom, and

other high performance applications.

The part has an on-chip PLL that locks to an input clock

presented on the REF pin. The PLL feedback is driven from

external FBK pin, so user has flexibility to choose any one of the

outputs as feedback input and connect it to FBK pin. The

input-to-output skew is less than 250 ps and output-to-output

skew is less than 200 ps.

The CY2308 has two banks of four outputs each that is controlled

by the select inputs as shown in the table Select Input Decoding

on page 3. If all output clocks are not required, Bank B is

three-stated. The input clock is directly applied to the output for

chip and system testing purposes by the select inputs.

The CY2308 PLL enters a power down state when there are no

rising edges on the REF input. In this mode, all outputs are

three-stated and the PLL is turned off resulting in less than 25

A

of current draw. The PLL shuts down in two additional cases as

shown in the table Select Input Decoding on page 3.

Multiple CY2308 devices accept the same input clock and

distribute it in a system. In this case, the skew between the

outputs of two devices is less than 700 ps.

The CY2308 is available in five different configurations as shown

in the table Available CY2308 Configurations on page 4.

■ The CY2308–1 is the base part where the output frequencies

equal the reference if there is no counter in the feedback path.

The CY2308–1H is the high drive version of the –1 and rise

and fall times on this device are much faster.

■ The CY2308–2 enables the user to obtain 2x and 1x

frequencies on each output bank. The exact configuration and

output frequencies depend on the user’s selection of output

that drives the feedback pin.

■ The CY2308–3 enables the user to obtain 4x and 2x

frequencies on the outputs.

■ The CY2308–4 enables the user to obtain 2x clocks on all

outputs. Thus, the part is extremely versatile and is used in a

variety of applications.

■ The CY2308–5H is a high drive version with REF/2 on both

banks.

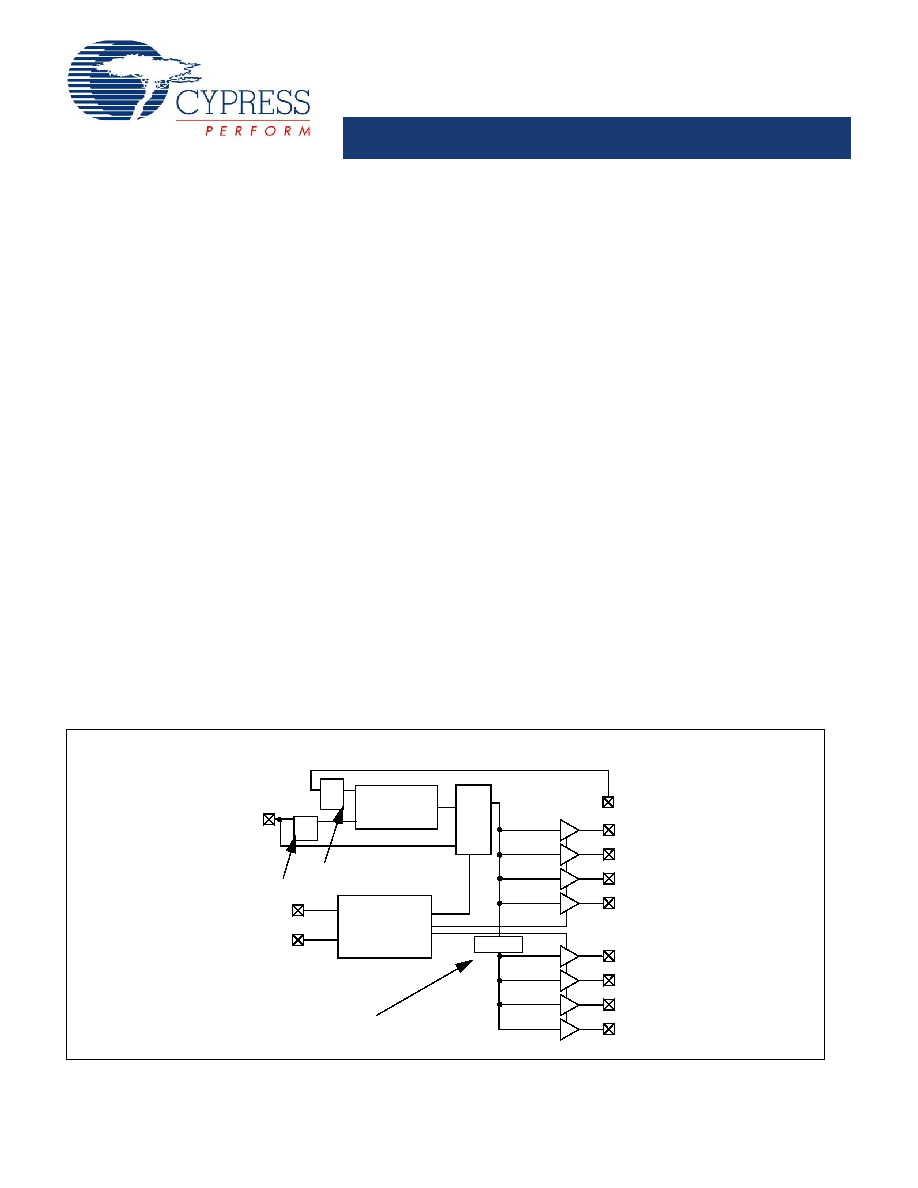

REF

CLKA1

CLKA2

CLKA3

CLKA4

FBK

PLL

MUX

Select Input

Decoding

S2

S1

CLKB1

CLKB2

CLKB3

CLKB4

/2

Extra Divider (–2, –3)

/2

Extra Divider (–3, –4)

Extra Divider (–5H)

/2

Logic Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| CY2308SI-4 | 3.3V Zero Delay Buffer |

| CY2308 | 3.3V Zero Delay Buffer |

| CY2309AZI-1H | 2309 SERIES, PLL BASED CLOCK DRIVER, 9 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| CY23S09SXC-1T | 23S SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| CY2DP818ZXCT | 2DP SERIES, LOW SKEW CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO38 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY2308SI-2[19] | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:3.3 V Zero Delay Buffer |

| CY2308SI-2T | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Driver Single 10MHz to 133MHz 16-Pin SOIC T/R |

| CY2308SI-2T[19] | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:3.3 V Zero Delay Buffer |

| CY2308SI-3 | 功能描述:IC CLK ZDB 8OUT 133MHZ 16SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| CY2308SI-3T | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Driver Single 10MHz to 133MHz 16-Pin SOIC T/R 制造商:Rochester Electronics LLC 功能描述:3.3VPLL ZERO DELAY CLOCK MULTIPLEXER SOIC 16 - Bulk |

发布紧急采购,3分钟左右您将得到回复。