- 您现在的位置:买卖IC网 > PDF目录295376 > CY7C09449PV Memory PDF资料下载

参数资料

| 型号: | CY7C09449PV |

| 英文描述: | Memory |

| 中文描述: | 内存 |

| 文件页数: | 18/20页 |

| 文件大小: | 301K |

| 代理商: | CY7C09449PV |

CY7C138AV/144AV/006AV

CY7C139AV/145AV/016AV

CY7C007AV/017AV

Document #: 38-06051 Rev. *A

Page 7 of 20

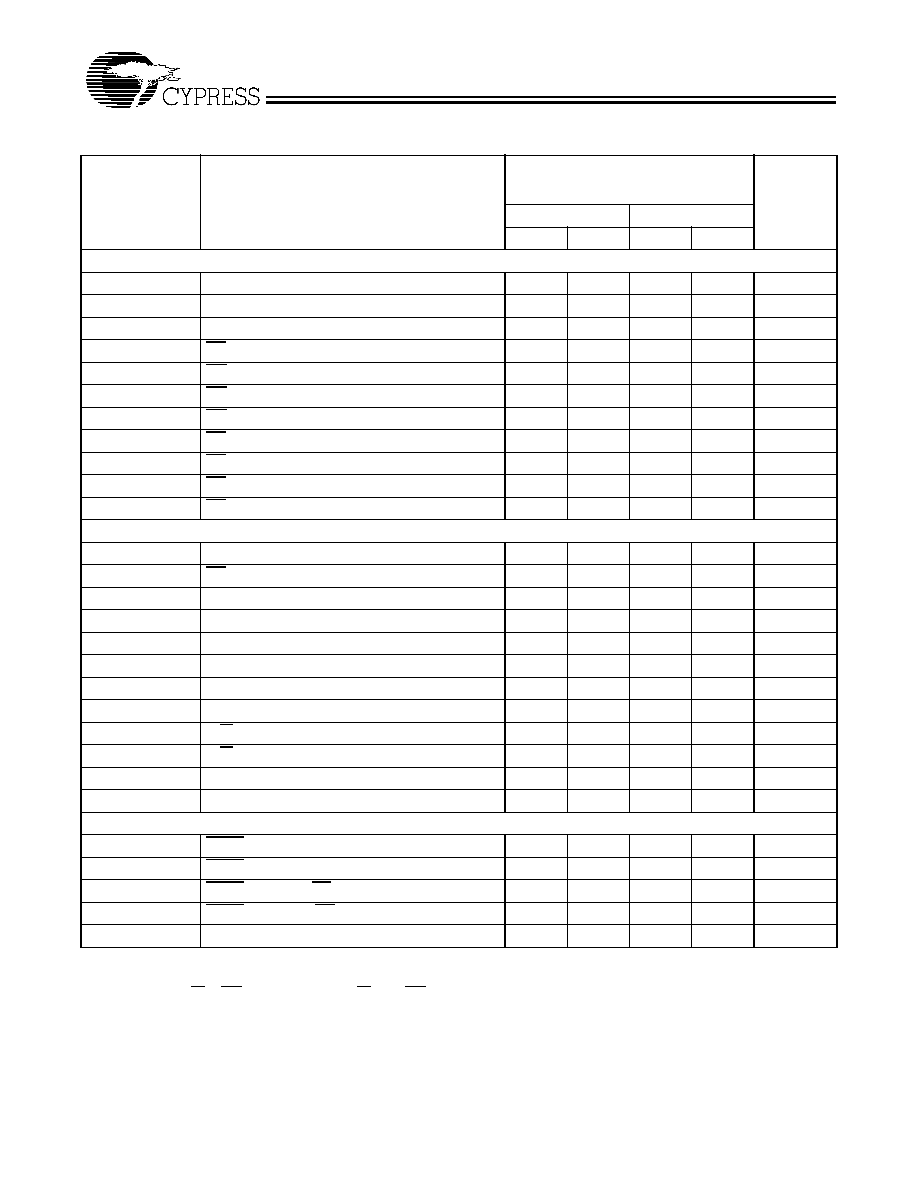

Switching Characteristics Over the Operating Range[15]

Parameter

Description

CY7C138AV/144AV/006AV

CY7C139AV/145AV/016AV

CY7C007AV/017AV

Unit

-20

-25

Min.

Max.

Min.

Max.

READ CYCLE

tRC

Read Cycle Time

20

25

ns

tAA

Address to Data Valid

20

25

ns

tOHA

Output Hold From Address Change

3

ns

tACE

[16]

CE LOW to Data Valid

20

25

ns

tDOE

OE LOW to Data Valid

12

13

ns

tLZOE

[17, 18, 19]

OE Low to Low Z

3

ns

tHZOE

[17, 18, 19]

OE HIGH to High Z

12

15

ns

tLZCE

[17, 18, 19]

CE LOW to Low Z

3

ns

tHZCE

[17, 18, 19]

CE HIGH to High Z

12

15

ns

tPU

[19]

CE LOW to Power-Up

0

ns

tPD

[19]

CE HIGH to Power-Down

20

25

ns

WRITE CYCLE

tWC

Write Cycle Time

20

25

ns

tSCE

[16]

CE LOW to Write End

16

20

ns

tAW

Address Valid to Write End

16

20

ns

tHA

Address Hold From Write End

0

ns

tSA

[16]

Address Set-Up to Write Start

0

ns

tPWE

Write Pulse Width

16

20

ns

tSD

Data Set-Up to Write End

12

15

ns

tHD

Data Hold From Write End

0

ns

tHZWE

[18, 19]

R/W LOW to High Z

12

15

ns

tLZWE

[18, 19]

R/W HIGH to Low Z

3

ns

tWDD

[20]

Write Pulse to Data Delay

40

50

ns

tDDD

[20]

Write Data Valid to Read Data Valid

30

35

ns

BUSY TIMING[21]

tBLA

BUSY LOW from Address Match

20

ns

tBHA

BUSY HIGH from Address Mismatch

20

ns

tBLC

BUSY LOW from CE LOW

20

ns

tBHC

BUSY HIGH from CE HIGH

16

17

ns

tPS

Port Set-Up for Priority

5

ns

Note:

15. Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified

IOI/IOH and 30-pF load capacitance.

16. To access RAM, CE=L, SEM=H. To access semaphore, CE=H and SEM=L. Either condition must be valid for the entire tSCE time.

17. At any given temperature and voltage condition for any given device, tHZCE is less than tLZCE and tHZOE is less than tLZOE.

18. Test conditions used are Load 3.

19. This parameter is guaranteed but not tested. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing

with Busy waveform.

20. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.

21. Test conditions used are Load 2.

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C09569V | Memory |

| CY7C09569V-100AC | SYNC SRAM|16KX36|CMOS|QFP|144PIN|PLASTIC |

| CY7C1413BV18-250BZXI | 2M X 18 QDR SRAM, 0.45 ns, PBGA165 |

| CY7C145-35JCR | 8K X 9 DUAL-PORT SRAM, 35 ns, PQCC68 |

| CY7C1472BV25-250BZXI | 4M X 18 ZBT SRAM, 3 ns, PBGA165 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C09449PVA-AC | 功能描述:IC SRAM 128KBIT 50MHZ 160LQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 产品变化通告:Product Discontinuation 05/Nov/2008 标准包装:84 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 ZBT 存储容量:4.5M(128K x 36) 速度:75ns 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 封装/外壳:119-BGA 供应商设备封装:119-PBGA(14x22) 包装:托盘 其它名称:71V3557SA75BGI |

| CY7C09449PV-AC | 功能描述:IC SRAM 128KBIT 50MHZ 160LQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:96 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:16M(2M x 8,1M x 16) 速度:70ns 接口:并联 电源电压:2.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 |

| CY7C09569V-100AC | 功能描述:IC SRAM 576KBIT 100MHZ 144LQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,500 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:1K (128 x 8) 速度:100kHz 接口:UNI/O?(单线) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-MSOP 包装:带卷 (TR) |

| CY7C09569V-100AXC | 功能描述:静态随机存取存储器 512K (16Kx36) 3.3v 100MHz Synch 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C09569V-100BBC | 功能描述:静态随机存取存储器 512K (16Kx36) 3.3v 100MHz Synch 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。