- 您现在的位置:买卖IC网 > PDF目录295373 > CY7C1157V18 (Cypress Semiconductor Corp.) 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) PDF资料下载

参数资料

| 型号: | CY7C1157V18 |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | 18-Mbit DDR-II+ SRAM 2-Word Burst Architecture (2.0 Cycle Read Latency) |

| 中文描述: | 18兆位的DDR - II SRAM的2字突发架构(2.0周期读写延迟) |

| 文件页数: | 14/27页 |

| 文件大小: | 969K |

| 代理商: | CY7C1157V18 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

CY7C1146V18

CY7C1157V18

CY7C1148V18

CY7C1150V18

Document Number: 001-06621 Rev. *C

Page 21 of 27

Capacitance

Tested initially and after any design or process change that may affect these parameters.

Parameter

Description

Test Conditions

Max

Unit

CIN

Input Capacitance

TA = 25°C, f = 1 MHz,

VDD = 1.8V

VDDQ = 1.5V

5pF

CCLK

Clock Input Capacitance

6

pF

CO

Output Capacitance

7pF

Thermal Resistance

Tested initially and after any design or process change that may affect these parameters.

Parameter

Description

Test Conditions

165 FBGA

Package

Unit

ΘJA

Thermal Resistance

(junction to ambient)

Test conditions follow standard test methods and

procedures for measuring thermal impedance, in

accordance with EIA/JESD51.

17.2

°C/W

ΘJC

Thermal Resistance

(junction to case)

4.15

°C/W

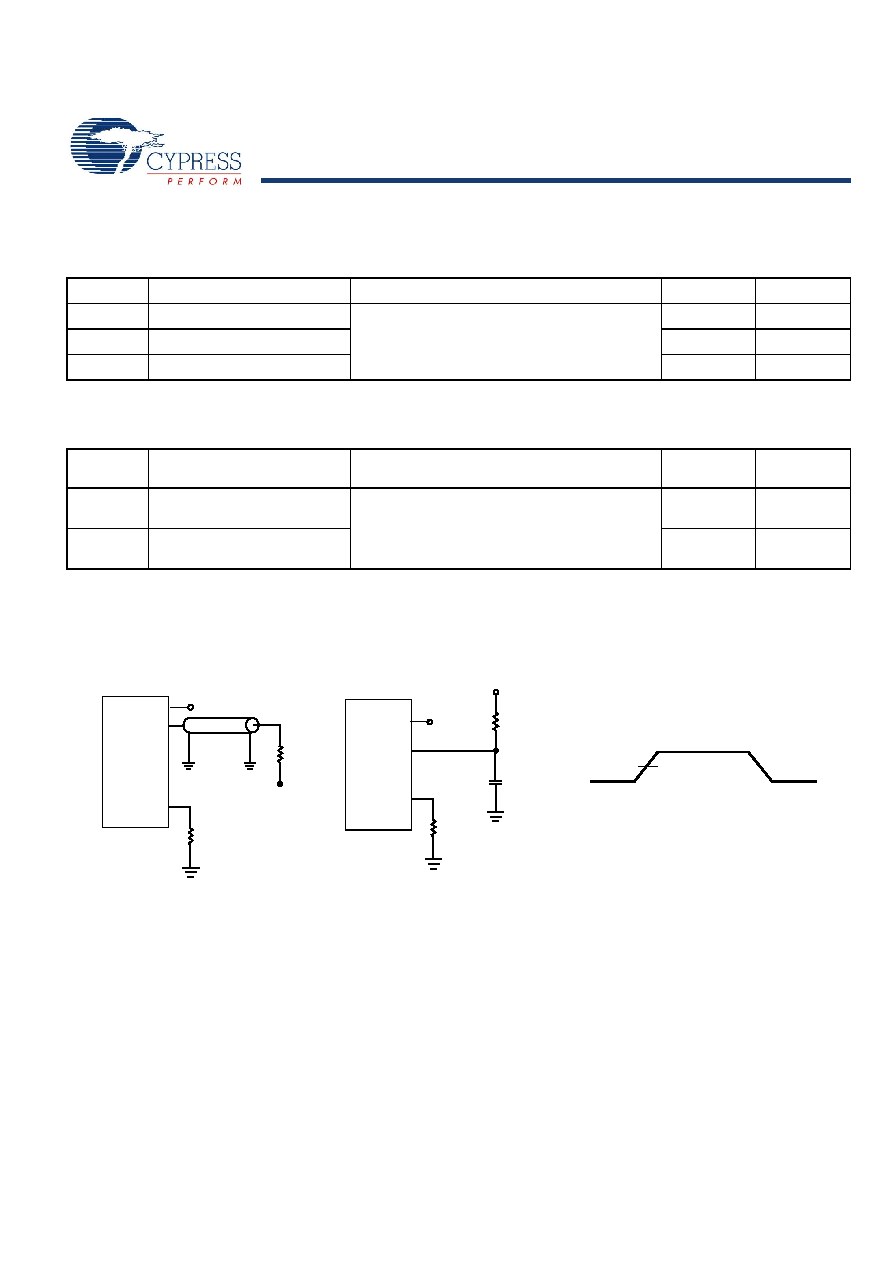

AC Test Loads and Waveforms

Figure 6. AC Test loads and Waveforms

1.25V

0.25V

R = 50

5pF

INCLUDING

JIG AND

SCOPE

ALL INPUT PULSES

DEVICE

RL = 50

Z0 = 50

VREF = 0.75V

[20]

0.75V

UNDER

TEST

0.75V

DEVICE

UNDER

TEST

OUTPUT

0.75V

VREF

OUTPUT

ZQ

(a)

SLEW RATE= 2 V/ns

RQ =

250

(b)

RQ =

250

Note

20. Unless otherwise noted, test conditions are based upon a signal transition time of 2V/ns, timing reference levels of 0.75V, VREF = 0.75V, RQ = 250, VDDQ = 1.5V,

input pulse levels of 0.25V to 1.25V, and output loading of the specified IOL/IOH and load capacitance shown in (a) of AC Test Loads.

[+] Feedback

相关PDF资料 |

PDF描述 |

|---|---|

| CY7C1161V18-300BZC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1161V18-300BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1161V18-333BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1161V18-333BZC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1161V18-300BZXI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY7C1163KV18-400BZI | 功能描述:静态随机存取存储器 18MB (1Mx18) 1.8v 400MHz DDR II 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C1163KV18-450BZC | 功能描述:静态随机存取存储器 18MB (1Mx18) 1.8v 450MHz DDR II 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C1163KV18-550BZC | 功能描述:静态随机存取存储器 18MB (1Mx18) 1.8v 550MHz DDR II 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C11651KV18-400BZC | 功能描述:静态随机存取存储器 Sync 静态随机存取存储器 QDR RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| CY7C11651KV18-400BZXC | 功能描述:IC SRAM 18MBIT 400MHZ 165-FPBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。