- 您现在的位置:买卖IC网 > PDF目录170654 > DAC5672AIPFBR (TEXAS INSTRUMENTS INC) DUAL, PARALLEL, WORD INPUT LOADING, 0.02 us SETTLING TIME, 14-BIT DAC, PQFP48 PDF资料下载

参数资料

| 型号: | DAC5672AIPFBR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | DUAL, PARALLEL, WORD INPUT LOADING, 0.02 us SETTLING TIME, 14-BIT DAC, PQFP48 |

| 封装: | GREEN, PLASTIC, TQFP-48 |

| 文件页数: | 6/26页 |

| 文件大小: | 1097K |

| 代理商: | DAC5672AIPFBR |

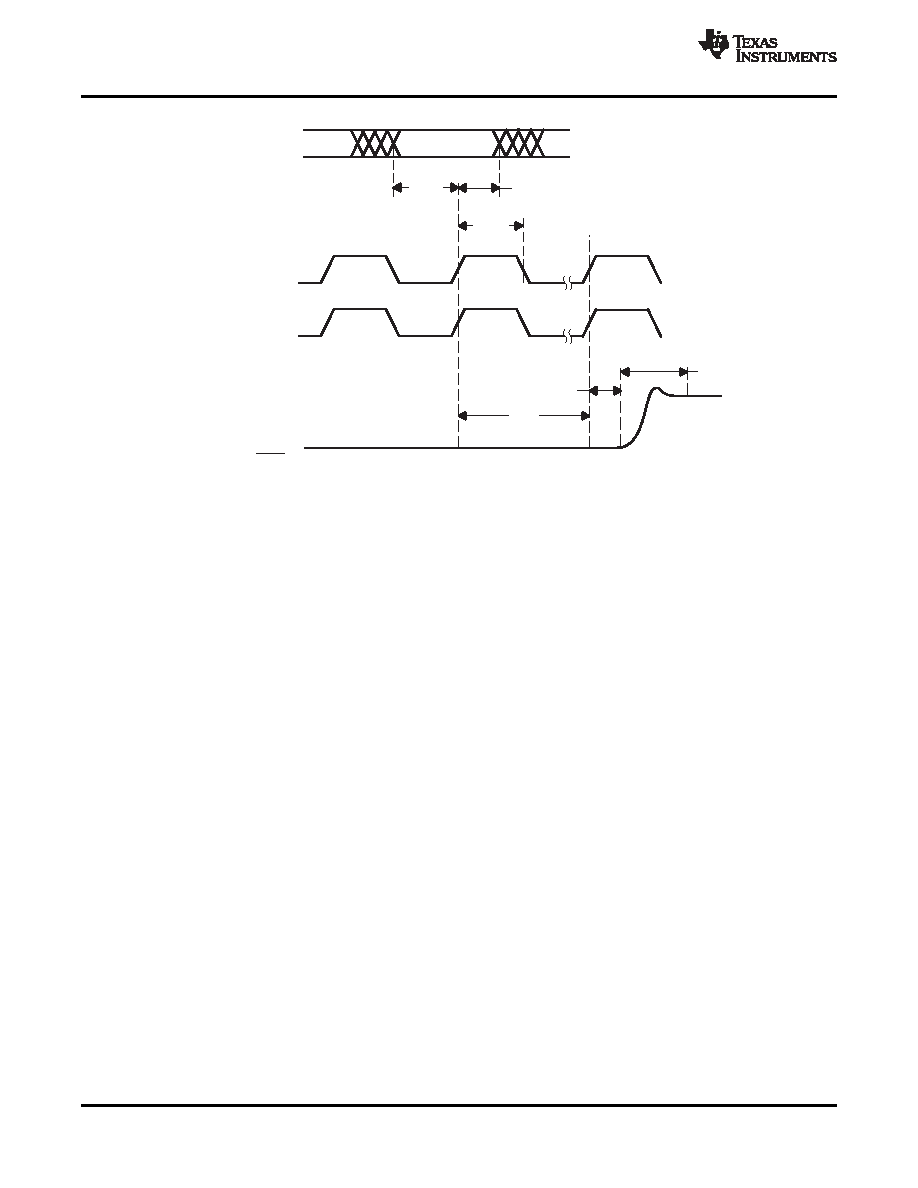

Valid Data

DA[13:0]/DB[13:0]

tsu

th

tlat

tpd

tsettle

WRTA/WRTB

CLKA/CLKB

IOUT

or

IOUT

t1ph

Single-Bus Interleaved Data Interface and Timing

SLAS528A – SEPTEMBER 2007 – REVISED MAY 2009................................................................................................................................................... www.ti.com

Figure 19. Dual-Bus Mode Operation

In single-bus interleaved mode, the MODE pin is connected to DGND. Figure 20 shows the timing diagram. In

interleaved mode, the A- and B-channels share the write input (WRTIQ) and update clock (CLKIQ and internal

CLKDACIQ). Multiplexing logic directs the input word at the A-channel input bus to either the A-channel input

latch (SELECTIQ is high) or to the B-channel input latch (SELECTIQ is low). When SELECTIQ is high, the data

value in the B-channel latch is retained by presenting the latch output data to its input again. When SELECTIQ is

low, the data value in the A-channel latch is retained by presenting the latch output data to its input.

In interleaved mode, the A-channel input data rate is twice the update rate of the DAC core. As in dual-bus

mode, it is important to maintain a correct sequence of write and clock inputs. The edge-triggered flip-flops latch

the A- and B-channel input words on the rising edge of the write input (WRTIQ). This data is presented to the A-

and B-DAC latches on the following falling edge of the write inputs. The DAC5672A clock input is divided by a

factor of two before it is presented to the DAC latches.

Correct pairing of the A- and B-channel data is done by RESETIQ. In interleaved mode, the clock input CLKIQ is

divided by two, which would translate to a non-deterministic relation between the rising edges of the CLKIQ and

CLKDACIQ. RESETIQ ensures, however, that the correct position of the rising edge of CLKDACIQ with respect

to the data at the input of the DAC latch is determined. CLKDACIQ is disabled (low) when RESETIQ is high.

14

Copyright 2007–2009, Texas Instruments Incorporated

Product Folder Link(s): DAC5672A

相关PDF资料 |

PDF描述 |

|---|---|

| DAC5687IPZP | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 |

| DAC5687IPZPG4 | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 |

| DAC5688IRGCTG4 | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQCC64 |

| DAC702LH | PARALLEL, WORD INPUT LOADING, 4 us SETTLING TIME, 16-BIT DAC, CDIP24 |

| DAC7545KUG4 | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC5672AIPFBRG4 | 功能描述:数模转换器- DAC 14B 275MSPS Dual DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5672-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL 14-BIT 200-MSPS DIGITAL-TO-ANALOG CONVERTER |

| DAC5672EVM | 功能描述:数据转换 IC 开发工具 DAC5672 Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| DAC5672IPFB | 功能描述:数模转换器- DAC Digital to Analog Converter RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5672IPFB | 制造商:Texas Instruments 功能描述:IC DAC 14BIT 275MSPS 制造商:Texas Instruments 功能描述:IC, DAC, 14BIT, 275MSPS, TQFP-48 |

发布紧急采购,3分钟左右您将得到回复。