- 您现在的位置:买卖IC网 > PDF目录170654 > DAC8564ICPWR (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 PDF资料下载

参数资料

| 型号: | DAC8564ICPWR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 |

| 封装: | GREEN, PLASTIC, TSSOP-16 |

| 文件页数: | 49/51页 |

| 文件大小: | 1549K |

| 代理商: | DAC8564ICPWR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页

SBAS403D

– JUNE 2007 – REVISED MAY 2011

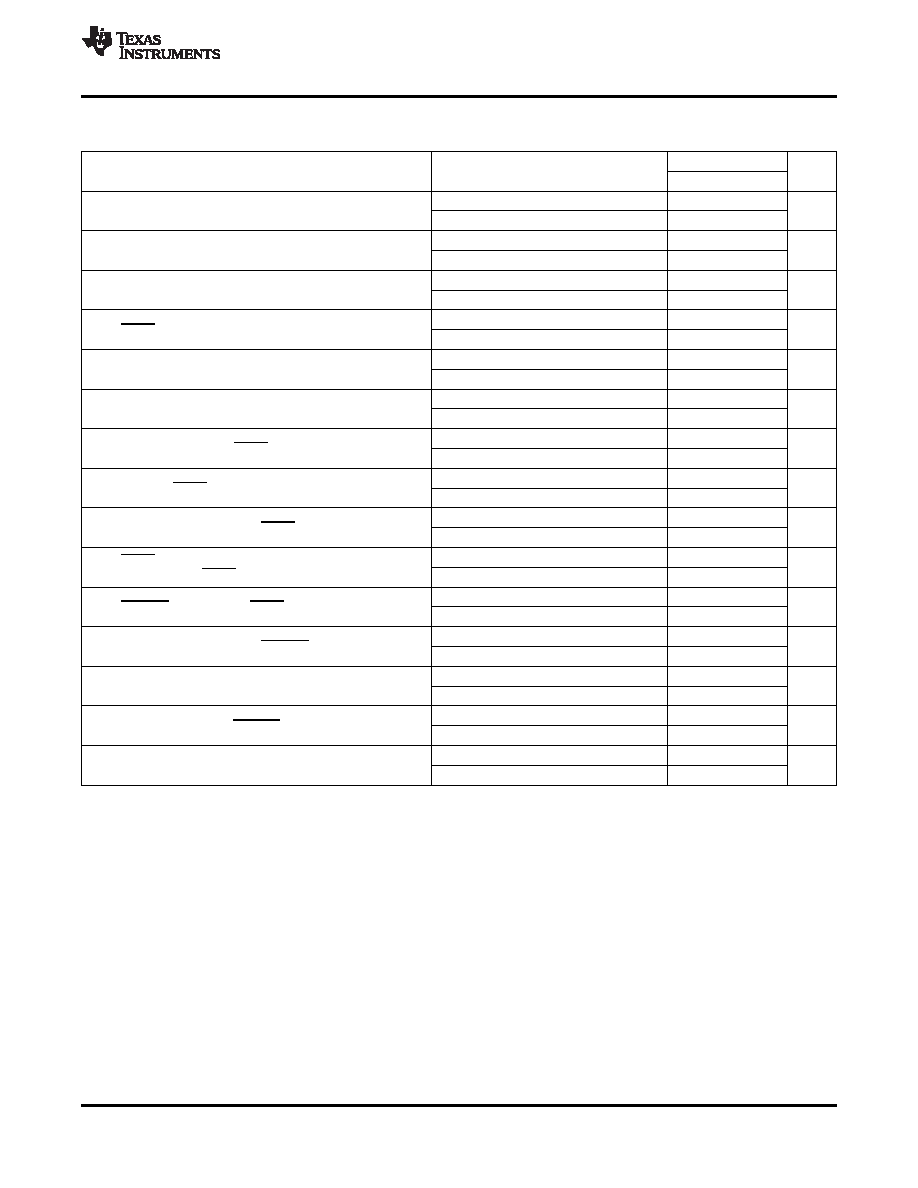

TIMING REQUIREMENTS

(1) (2)

At AVDD = IOVDD= 2.7V to 5.5V and –40°C to +105°C range (unless otherwise noted).

DAC8564

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

IOVDD = AVDD = 2.7V to 3.6V

40

t1

(3)

SCLK cycle time

ns

IOVDD = AVDD = 3.6V to 5.5V

20

IOVDD = AVDD = 2.7V to 3.6V

20

t2

SCLK HIGH time

ns

IOVDD = AVDD = 3.6V to 5.5V

10

IOVDD = AVDD = 2.7V to 3.6V

20

t3

SCLK LOW time

ns

IOVDD = AVDD = 3.6V to 5.5V

10

IOVDD = AVDD = 2.7V to 3.6V

0

t4

SYNC to SCLK rising edge setup time

ns

IOVDD = AVDD = 3.6V to 5.5V

0

IOVDD = AVDD = 2.7V to 3.6V

5

t5

Data setup time

ns

IOVDD = AVDD = 3.6V to 5.5V

5

IOVDD = AVDD = 2.7V to 3.6V

4.5

t6

Data hold time

ns

IOVDD = AVDD = 3.6V to 5.5V

4.5

IOVDD = AVDD = 2.7V to 3.6V

0

t7

SCLK falling edge to SYNC rising edge

ns

IOVDD = AVDD = 3.6V to 5.5V

0

IOVDD = AVDD = 2.7V to 3.6V

40

t8

Minimum SYNC HIGH time

ns

IOVDD = AVDD = 3.6V to 5.5V

20

IOVDD = AVDD = 2.7V to 3.6V

130

t9

24th SCLK falling edge to SYNC falling edge

ns

IOVDD = AVDD = 3.6V to 5.5V

130

IOVDD = AVDD = 2.7V to 3.6V

15

SYNC rising edge to 24th SCLK falling edge

t10

ns

(for successful SYNC interrupt)

IOVDD = AVDD = 3.6V to 5.5V

15

IOVDD = AVDD = 2.7V to 3.6V

15

t11

ENABLE falling edge to SYNC falling edge

ns

IOVDD = AVDD = 3.6V to 5.5V

15

IOVDD = AVDD = 2.7V to 3.6V

10

t12

24th SCLK falling edge to ENABLE rising edge

ns

IOVDD = AVDD = 3.6V to 5.5V

10

IOVDD = AVDD = 2.7V to 3.6V

50

t13

24th SCLK falling edge to LDAC rising edge

ns

IOVDD = AVDD = 3.6V to 5.5V

50

IOVDD = AVDD = 2.7V to 3.6V

10

t14

LDAC rising edge to ENABLE rising edge

ns

IOVDD = AVDD = 3.6V to 5.5V

10

IOVDD = AVDD = 2.7V to 3.6V

10

t15

LDAC HIGH time

ns

IOVDD = AVDD = 3.6V to 5.5V

10

(1)

All input signals are specified with tR = tF = 3ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

(2)

See the Serial Write Operation timing diagram.

(3)

Maximum SCLK frequency is 50MHz at IOVDD = VDD = 3.6V to 5.5V and 25MHz at IOVDD = AVDD = 2.7V to 3.6V.

Copyright

2007–2011, Texas Instruments Incorporated

7

相关PDF资料 |

PDF描述 |

|---|---|

| DAC8564IDPW | SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 |

| DAC8564IAPWG4 | SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 |

| DAC8564IAPWRG4 | SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 |

| DAC8564IBPWG4 | SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 |

| DAC8564IBPWRG4 | SERIAL INPUT LOADING, 12 us SETTLING TIME, 16-BIT DAC, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC8564ICPWRG4 | 功能描述:数模转换器- DAC 16B vOut DAC quad chan Ultra Lo glitch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC8564IDPW | 功能描述:数模转换器- DAC 16B Quad Ch Ultra-Lo Glitch Vltg Output RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC8564IDPWG4 | 功能描述:数模转换器- DAC 16B vOut DAC quad chan Ultra Lo glitch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC8564IDPWR | 功能描述:数模转换器- DAC 16B Quad Ch Ultra-Lo Glitch Vltg Output RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC8564IDPWRG4 | 功能描述:数模转换器- DAC 16B vOut DAC quad chan Ultra Lo glitch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。