- 您现在的位置:买卖IC网 > PDF目录17086 > DC1110A (Linear Technology)BOARD DAC LTC2751-16 PDF资料下载

参数资料

| 型号: | DC1110A |

| 厂商: | Linear Technology |

| 文件页数: | 5/22页 |

| 文件大小: | 0K |

| 描述: | BOARD DAC LTC2751-16 |

| 软件下载: | QuikEval System |

| 设计资源: | DC1110A Design File DC1110A Schematic |

| 标准包装: | 1 |

| 系列: | QuikEval™, SoftSpan™ |

| DAC 的数量: | 1 |

| 位数: | 16 |

| 数据接口: | 并联 |

| 设置时间: | 2µs |

| DAC 型: | 电流 |

| 工作温度: | 0°C ~ 70°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | LTC2751-16 |

| 相关产品: | DC590B-ND - BOARD DEMO USB SERIAL CONTROLLER LTC2751BIUHF-16#TRPBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751BIUHF-16#PBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751BCUHF-16#TRPBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751BCUHF-16#PBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751AIUHF-16#TRPBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751AIUHF-16#PBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751ACUHF-16#TRPBF-ND - IC DAC 16BIT CUR OUT 38-QFN LTC2751ACUHF-16#PBF-ND - IC DAC 16BIT CUR OUT 38-QFN |

LTC2751

13

2751fa

operaTion

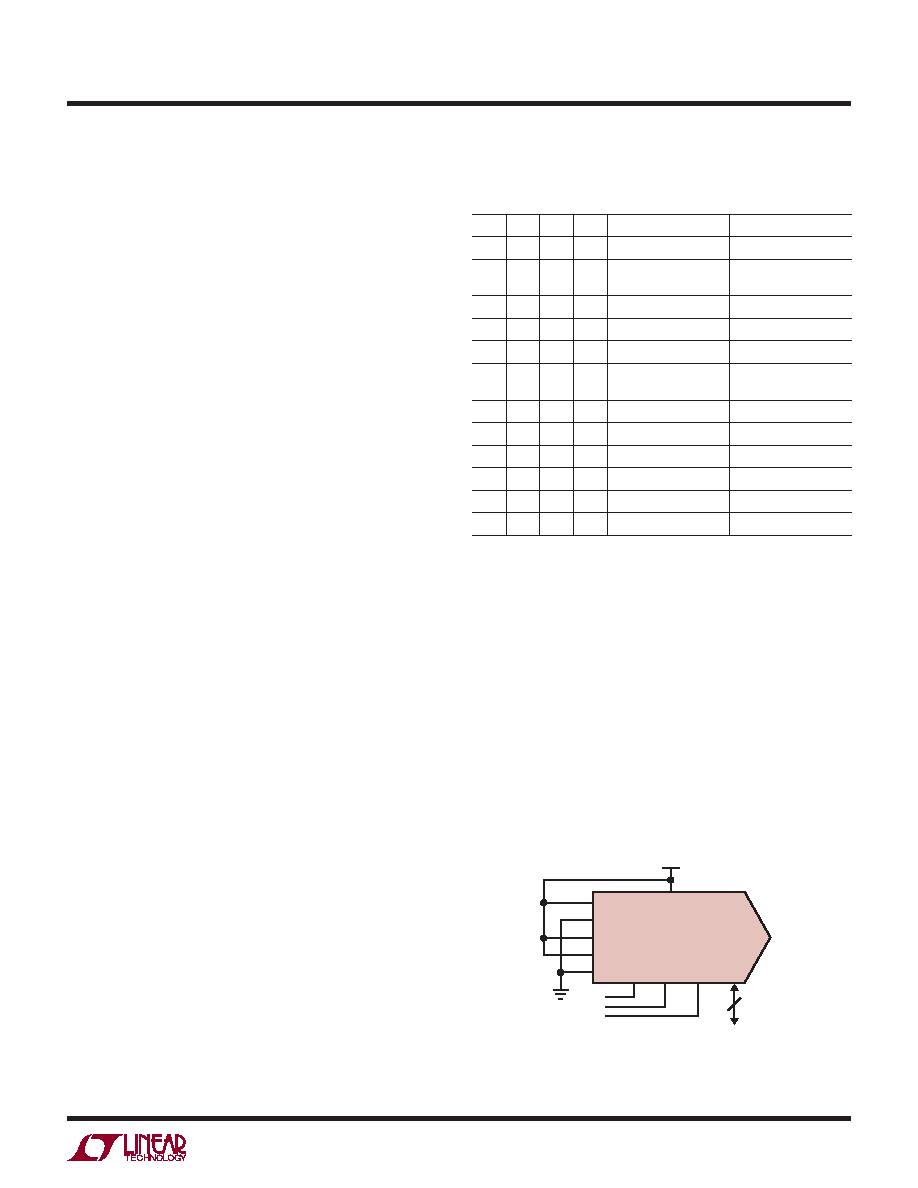

Table 1 shows the functions of the LTC2751.

Table 1. Write, Update and Read Functions

READ D/S

WR UPD

SPAN I/O

DATA I/O

0

-

Write to Input Register

0

1

-

Write/Update

(Transparent)

0

1

0

-

0

1

Update DAC Register Update DAC Register

0

1

0

Write to Input Register

-

0

1

0

1

Write/Update

(Transparent)

-

0

1

0

-

0

1

Update DAC register

Update DAC Register

1

0

X

0

-

Read Input Register

1

0

X

1

-

Read DAC Register

1

X

0

Read Input Register

-

1

X

1

Read DAC Register

-

X = Don’t Care

Manual Span Configuration

Multipleoutputrangesarenotneededinsomeapplications.

ToconfiguretheLTC2751forsingle-spanoperation,tiethe

MSPAN pin to VDD and the D/S pin to GND. The desired

output range is then specified by the span I/O pins (S0, S1

and S2) as usual, but the pins are programmed by tying

directly to GND or VDD (see Figure 1 and Table 2). In this

configuration, the part will initialize to the chosen output

range at power-up, with VOUT = 0V.

When configured for manual span operation, span pin

readback is disabled.

Write and Update Operations

The data input register is loaded directly from a 16-bit

microprocessor bus by holding the D/S pin low and then

pulsing the WR pin low. The second register (DAC regis-

ter) is loaded by pulsing the UPD pin high, which copies

the data held in the input register into the DAC register.

Note that updates always include both data and span; but

the DAC register values will not change unless the input

register values have been changed by writing.

Loadingthespaninputregisterisaccomplishedinasimilar

manner, by holding the D/S pin high and then bringing

the WR pin low. The span and data register structures

are the same except for the number of parallel bits—the

span registers have three bits, while the data registers

have 12, 14, or 16 bits.

To make both registers transparent for flowthrough mode,

tie WR low and UPD high. However, this defeats the de-

glitcher operation and output glitch impulse may increase.

ThedeglitcherisactivatedontherisingedgeoftheUPDpin.

The interface also allows the use of the input and DAC

registers in a master-slave, or edge-triggered, configura-

tion. This mode of operation occurs when WR and UPD

are tied together and driven by a single clock signal. The

data bits are loaded into the input register on the falling

edge of the clock and then loaded into the DAC register

on the rising edge.

The separation of data and span for write and read opera-

tions makes it possible to control both data and span on

one 16-bit wide data bus by allowing span pins S2 to S0

to share bus lines with the data LSBs (D2 to D0). Since

no write or read operation includes both span and data,

there cannot be a conflict.

The asynchronous clear pin resets the LTC2751 to 0V

(zero-, half- or quarter-scale code) in any output range.

CLR resets both the input and DAC data registers, while

leaving the span registers undisturbed.

These devices also have a power-on reset. If configured

for SoftSpan operation, the part initializes to zero scale in

the 0V to 5V output range. If configured for single-span

operation, the part initializes to the zero-volt code in the

chosen output range.

Figure 1. Configuring the LTC2751 for

Single-Span Operation (±10V Range)

LTC2751-16

MSPAN

S2

S1

S0

D/S

VDD

2751 F01

WR UPD READ

DATA I/O

16

VDD

相关PDF资料 |

PDF描述 |

|---|---|

| EEM36DRSI | CONN EDGECARD 72POS DIP .156 SLD |

| RP40-2405SGW/N-HC | CONV DC/DC 40W 9-36VIN 05VOUT |

| R-532.5DA | CONV DC/DC 3A 4.5-18VIN 2.5V |

| 0210390972 | CABLE JUMPER 1MM .127M 27POS |

| EEM36DRMI | CONN EDGECARD 72POS .156 SQ WW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC1111 | 制造商:TUTH 功能描述: |

| DC-111-1 | 制造商:INTRONICS 制造商全称:INTRONICS 功能描述:1 WATT SINGLE OUTPUT DC-DC CONVERTERS |

| DC1111A | 功能描述:BOARD DAC LTC2753-16 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:QuikEval™, SoftSpan™ 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| DC1111C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:D_1111C Series, Ultra Compact InGaN/SiC SMT LED |

| DC1111C-TR | 功能描述:LED BLUISH-GREEN 0603 SMD RoHS:是 类别:光电元件 >> LED - 1111C 标准包装:500 系列:Screenmaster® 颜色:琥珀 Millicandela 等级:2260mcd 正向电压:2.1V 电流 - 测试:20mA 波长 - 主:590nm 波长 - 峰值:- 视角:- 透镜类型:散射,有色 透镜样式/尺寸:圆顶椭圆,5.1mm x 3.7mm 封装/外壳:径向 尺寸/尺寸:- 高度:7.00mm 安装类型:通孔 包装:散装 在特定电流下的光通量 - 测试:- |

发布紧急采购,3分钟左右您将得到回复。