- 您现在的位置:买卖IC网 > PDF目录19023 > DC1369A-C (Linear Technology)BOARD DEMO 80MSPS LTC2259-14 PDF资料下载

参数资料

| 型号: | DC1369A-C |

| 厂商: | Linear Technology |

| 文件页数: | 14/34页 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO 80MSPS LTC2259-14 |

| 软件下载: | QuikEval II System |

| 设计资源: | DC1369A Design Files |

| 标准包装: | 1 |

| 系列: | * |

| 相关产品: | DC890B-ND - BOARD USB DATA COLLECTION |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

21

226114fc

LTC2261-14

LTC2260-14/LTC2259-14

For more information www.linear.com/LTC2261-14

applicaTions inForMaTion

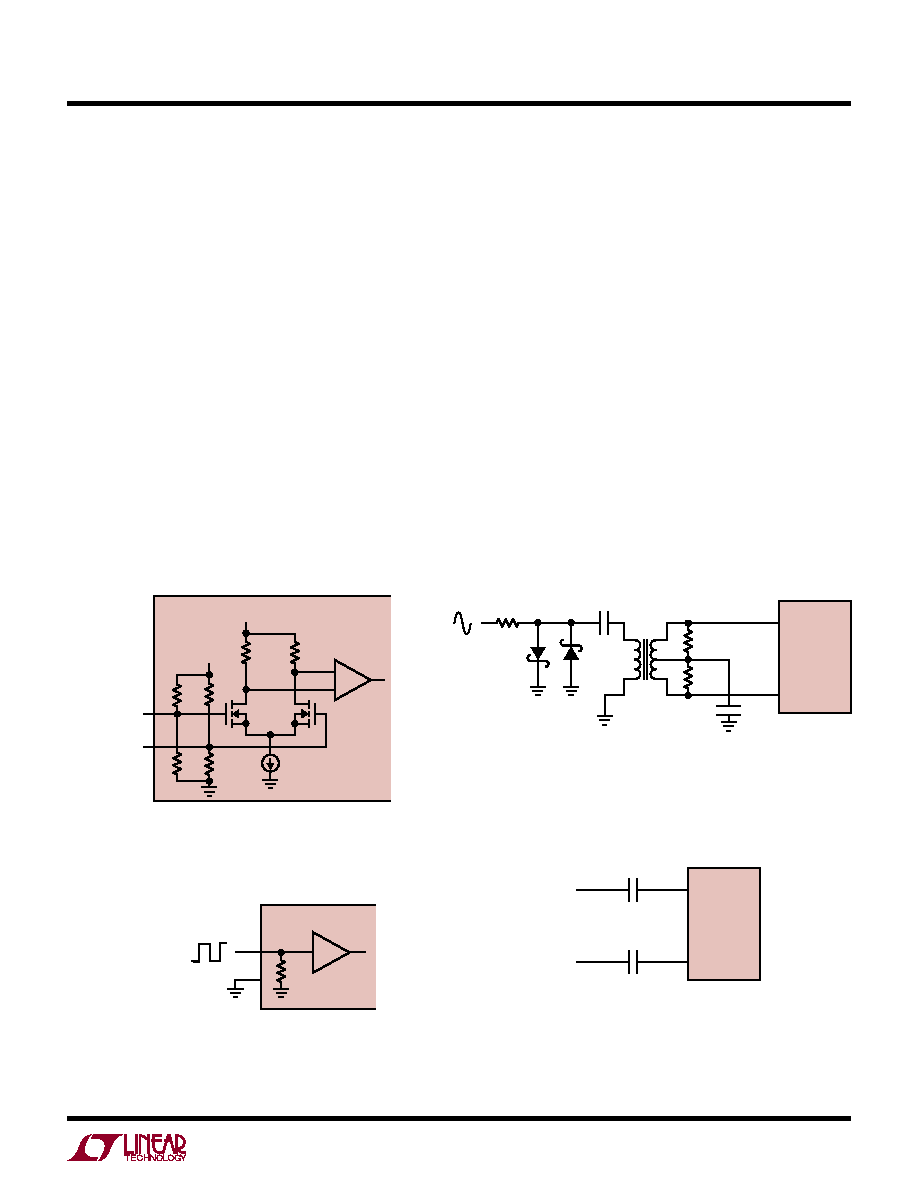

Encode Input

The signal quality of the encode inputs strongly affects

the A/D noise performance. The encode inputs should

be treated as analog signals—do not route them next to

digital traces on the circuit board. There are two modes

of operation for the encode inputs: the differential encode

mode (Figure 10) and the single-ended encode mode

(Figure 11).

The differential encode mode is recommended for sinu-

soidal, PECL or LVDS encode inputs (Figures 12, 13). The

encode inputs are internally biased to 1.2V through 10k

equivalent resistance. The encode inputs can be taken

above VDD (up to 3.6V), and the common mode range

is from 1.1V to 1.6V. In the differential encode mode,

ENC– should stay at least 200mV above ground to avoid

falsely triggering the single-ended encode mode. For good

jitter performance ENC+ and ENC– should have fast rise

and fall times.

Thesingle-endedencodemodeshouldbeusedwithCMOS

encode inputs. To select this mode, ENC– is connected

to ground and ENC+ is driven with a square wave encode

input. ENC+ can be taken above VDD (up to 3.6V) so 1.8V

to3.3VCMOSlogiclevelscanbeused.TheENC+threshold

is 0.9V. For good jitter performance ENC+ should have fast

rise and fall times.

Clock Duty Cycle Stabilizer

For good performance the encode signal should have a

50%(±5%) duty cycle. If the optional clock duty cycle

stabilizer circuit is enabled, the encode duty cycle can

vary from 30% to 70% and the duty cycle stabilizer will

maintain a constant 50% internal duty cycle. If the encode

signal changes frequency or is turned off, the duty cycle

stabilizer circuit requires one hundred clock cycles to lock

onto the input clock. The duty cycle stabilizer is enabled

by mode control register A2 (serial programming mode),

or by CS (parallel programming mode).

VDD

LTC2261-14

226114 F10

ENC–

ENC+

15k

VDD

DIFFERENTIAL

COMPARATOR

30k

Figure 10. Equivalent Encode Input Circuit

for Differential Encode Mode

30k

ENC+

ENC–

226114 F11

0V

1.8V TO 3.3V

LTC2261-14

CMOS LOGIC

BUFFER

Figure 11. Equivalent Encode Input Circuit

for Single-Ended Encode Mode

100

25

D1

ENC+

ENC–

0.1F

T1: COILCRAFT WBC4 - 1WL

D1: AVAGO HSMS - 2822

RESISTORS, CAPACITORS ARE 0402 PACKAGE SIZE

226114 F12

LTC2261-14

T1

1:4

Figure 12. Sinusoidal Encode Drive

ENC+

ENC–

PECL OR

LVDS

CLOCK

0.1F

226114 F13

LTC2261-14

Figure 13. PECL or LVDS Encode Drive

相关PDF资料 |

PDF描述 |

|---|---|

| 5AB | LAMP NEON WIRE TERMINAL NE-23 |

| DC1369A-H | BOARD DEMO 105MSPS LTC2260-12 |

| CM381 | LAMP T1-3/4 FLANGE BASE .2A |

| A0213Y | 30MM IND CTRL PB OPERATOR |

| CM380 | LAMP T1-3/4 FLANGE BASE .04A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC1369A-D | 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC1371 & DC1075 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC1371 & DC1075; Silicon Manufacturer:Linear Technology; Silicon Core Number:LTC2258-14; Kit Application Type:Data Converter; Application Sub Type:ADC; Kit Contents:Board, Guide |

| DC1369A-E | 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC1371 & DC1075 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC1371 & DC1075; Silicon Manufacturer:Linear Technology; Silicon Core Number:LTC2257-14; Kit Application Type:Data Converter; Application Sub Type:ADC; Kit Contents:Board, Guide |

| DC1369A-F | 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC1371 & DC1075 制造商:Linear Technology 功能描述:14BIT ADC Eval Brd, Rq. DC1371 & DC1075; Silicon Manufacturer:Linear Technology; Silicon Core Number:LTC2256-14; Kit Application Type:Data Converter; Application Sub Type:ADC; Kit Contents:Board, Guide |

| DC1369A-G | 功能描述:BOARD DEMO 125MSPS LTC2261-12 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

| DC1369A-H | 功能描述:BOARD DEMO 105MSPS LTC2260-12 RoHS:是 类别:未定义的类别 >> 其它 系列:* 标准包装:1 系列:* 其它名称:MS305720A |

发布紧急采购,3分钟左右您将得到回复。