- 您现在的位置:买卖IC网 > PDF目录16542 > DC1562A-H (Linear Technology)BOARD EVAL LTC6993-2 PDF资料下载

参数资料

| 型号: | DC1562A-H |

| 厂商: | Linear Technology |

| 文件页数: | 10/26页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL LTC6993-2 |

| 设计资源: | DC1562A Design Files DC1562A Schematic |

| 特色产品: | TimerBlox? |

| 标准包装: | 1 |

| 系列: | TimerBlox® |

| 主要目的: | 定时,单稳多谐振荡器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | LTC6993-2 |

| 主要属性: | 上升沿触发器,可再触发 |

| 次要属性: | 2.25 V ~ 5.5 V 电源 |

| 已供物品: | 板 |

LTC6993-1/LTC6993-2

LTC6993-3/LTC6993-4

18

69931234fb

ISET Extremes (Master Oscillator Frequency Extremes)

When operating with ISET outside of the recommended

1.25A to 20A range, the master oscillator operates

outside of the 62.5kHz to 1MHz range in which it is most

accurate.

The oscillator will still function with reduced accuracy for

ISET < 1.25A. At approximately 500nA, the oscillator will

stop. Under this condition, the output pulse can still be

initiated, but will not terminate until ISET increases and

the master oscillator starts again.

At the other extreme, it is not recommended to operate

the master oscillator beyond 2MHz because the accuracy

of the DIV pin ADC will suffer.

Settling Time

Following a 2

× or 0.5× step change in ISET, the output

pulse width takes approximately six master clock cycles

(6 tMASTER) to settle to within 1% of the final value. An

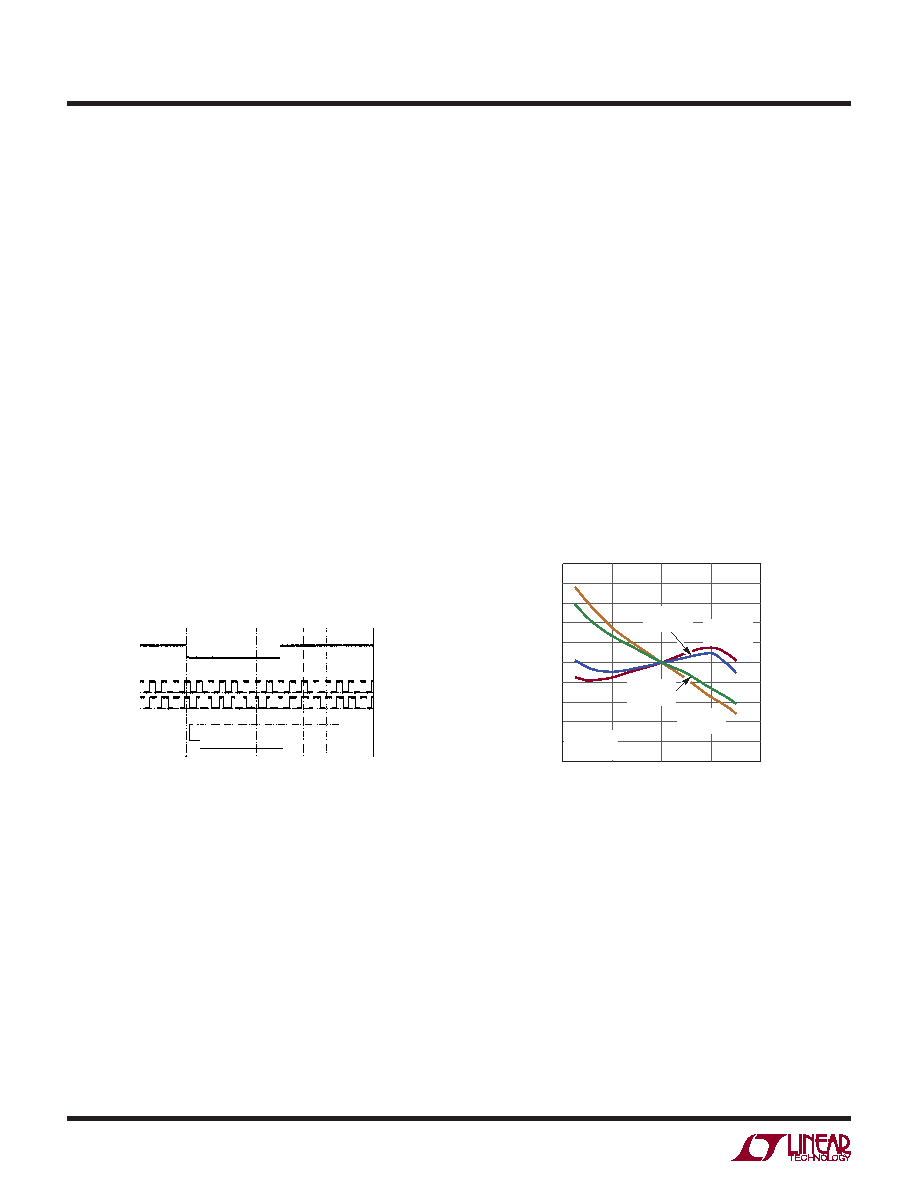

exampleisshowninFigure10,usingthecircuitinFigure 8.

Coupling Error

The current sourced by the SET pin is used to bias the

internal master oscillator. The LTC6993 responds to

changesinISETalmostimmediately,whichprovidesexcel-

lent settling time. However, this fast response also makes

the SET pin sensitive to coupling from digital signals, such

as the TRIG input.

Even an excellent layout will allow some coupling between

TRIG and SET. Additional error is included in the speci-

fied accuracy for NDIV = 1 to account for this. Figure 11

shows that ÷1 supply variation is dependent on coupling

from rising or falling trigger inputs and, to a lesser extent,

output polarity.

A very poor layout can actually degrade performance

further. The PCB layout should avoid routing SET next to

TRIG (or any other fast-edge, wide-swing signal).

APPLICATIONS INFORMATION

Figure 10. Typical Settling Time

VCTRL

2V/DIV

TRIG

5V/DIV

OUT

5V/DIV

PULSE WIDTH

2s/DIV

LTC6993-1

V+ = 3.3V

DIVCODE = 0

RSET = 200k

RMOD = 464k

tOUT = 3s AND 6s

20s/DIV

69931234 F10

SUPPLY (V)

2

–1.0

DRIFT

(%)

–0.8

–0.4

–0.2

0

1.0

0.4

3

4

69931234 F11

–0.6

0.6

0.8

0.2

5

6

RSET = 50k

NDIV = 1

LTC6993-1

POL = 0

LTC6993-1

POL = 1

LTC6993-3

POL = 1

LTC6993-3

POL = 0

Figure 11. tOUT Drift vs Supply Voltage

相关PDF资料 |

PDF描述 |

|---|---|

| ECE-T2WP102FA | CAP ALUM 1000UF 450V 20% SNAP |

| GMC06DRTN-S734 | CONN EDGECARD 12POS DIP .100 SLD |

| CE201210-5N6K | INDUCTOR 5.6NH 300MA SMD |

| GCM24DCBS-S189 | CONN EDGECARD 48POS R/A .156 SLD |

| A3CCB-3406M | IDC CABLE- AKC34B/AE34M/AKC34B |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC1562A-I | 功能描述:BOARD EVAL LTC6993-3 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:TimerBlox® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP |

| DC1562A-J | 功能描述:BOARD EVAL LTC6993-4 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:TimerBlox® 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| DC1562A-K | 功能描述:BOARD EVAL LTC6994-1 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:TimerBlox® 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| DC1562A-L | 功能描述:BOARD EVAL LTC6994-2 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:TimerBlox® 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| DC1562B-B | 制造商:Linear Technology 功能描述:LTC6991 DEMO BOARD 1Hz (1s) Fixed Frequenc |

发布紧急采购,3分钟左右您将得到回复。