- 您现在的位置:买卖IC网 > Datasheet目录320 > DK-N2EVAL-3C25N (Altera)KIT DEV NIOS II CYCLONE III ED. Datasheet资料下载

参数资料

| 型号: | DK-N2EVAL-3C25N |

| 厂商: | Altera |

| 文件页数: | 25/36页 |

| 文件大小: | 0K |

| 描述: | KIT DEV NIOS II CYCLONE III ED. |

| 产品培训模块: | Cyclone® III FPGA NiosII Embedded Processors Three Reasons to Use FPGA's in Industrial Designs |

| 特色产品: | Nios? II Embedded Evaluation Kit, Cyclone? III Edition |

| 标准包装: | 1 |

| 系列: | Cyclone® III |

| 类型: | FPGA |

| 适用于相关产品: | EP3C25 |

| 所含物品: | 开发板,模块和软件 |

| 产品目录页面: | 606 (CN2011-ZH PDF) |

| 相关产品: | 544-2565-ND - IC CYCLONE III FPGA 25K 324 FBGA 544-2564-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2563-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2562-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2561-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2560-ND - IC CYCLONE III FPGA 5K 256 UBGA 544-2559-ND - IC CYCLONE III FPGA 5K 164 MBGA 544-2558-ND - IC CYCLONE III FPGA 5K 256 FBGA 544-2557-ND - IC CYCLONE III FPGA 5K 144 EQFP 544-2556-ND - IC CYCLONE III FPGA 55K 484 UBGA 更多... |

| 其它名称: | 544-2411 DK-N2EVAL-3C25N-OB DK-NIOSEVAL-3C25N NEEK |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

�

�Measuring� Power� on� the� Cyclone� III� Starter� Board�

�1�

�To� obtain� the� power� (P)� in� milliwatts,� measure� <� Measured�

�Voltage� >� (the� voltage� across� the� sense� resistors� at� JP6� or� JP3)� in�

�mV� and� calculate� the� nominal� power� using� the� equation:�

�P� =� 100� x� <� Measured� Voltage� >� x� <� Supply� Voltage� >�

�where� <� Supply� Voltage� >� is� 1.2� V� for� JP6� and� 2.5� V� for� JP3.�

�You� can� use� the� four� input� buttons� to� advance� through� the� various� power�

�state� as� outlined� in� Table� 4–2� .� Notice� how� current� increases� as� frequency�

�and� resource� usage� increase.�

�You� can� also� measure� the� I/O� power� consumed� by� measuring� the� voltage�

�across� sense-resistor� JP3� when� Button� 4� is� pressed� and� held.� Because� this�

�2.5-V� power� rail� is� shared� with� other� devices,� there� is� a� nominal� 100� mW�

�that� must� be� subtracted� from� the� calculated� I/O� power� to� obtain� the�

�FPGA� I/O� power.�

�The� number� of� I/O� pins� used� is� controlled� by� the� resource� state� (shown�

�in� Tables� 4–2� and� 4–3� ).� For� each� increment� in� resources,� 16� additional� I/O�

�pins� are� added� (refer� to� Table� 4–4� ).�

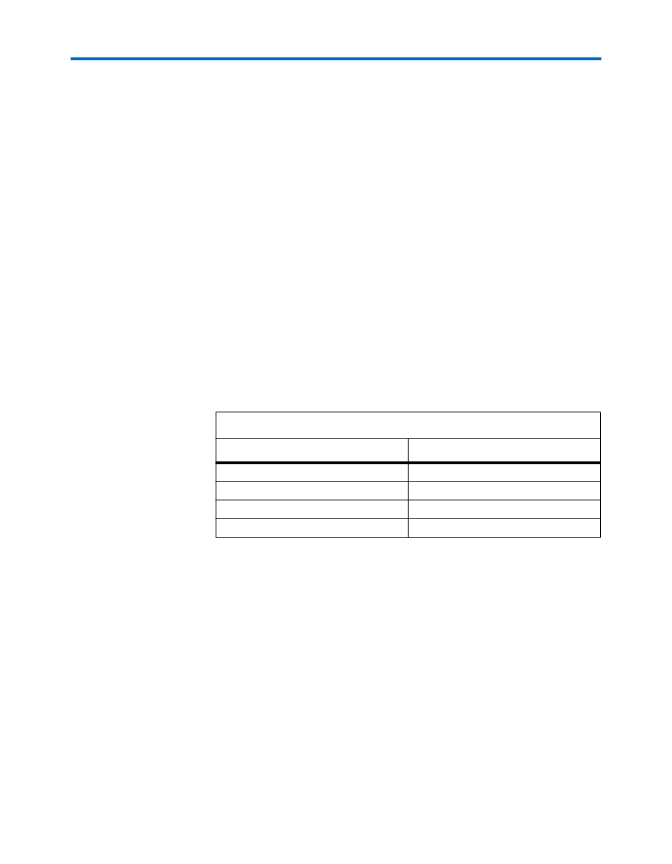

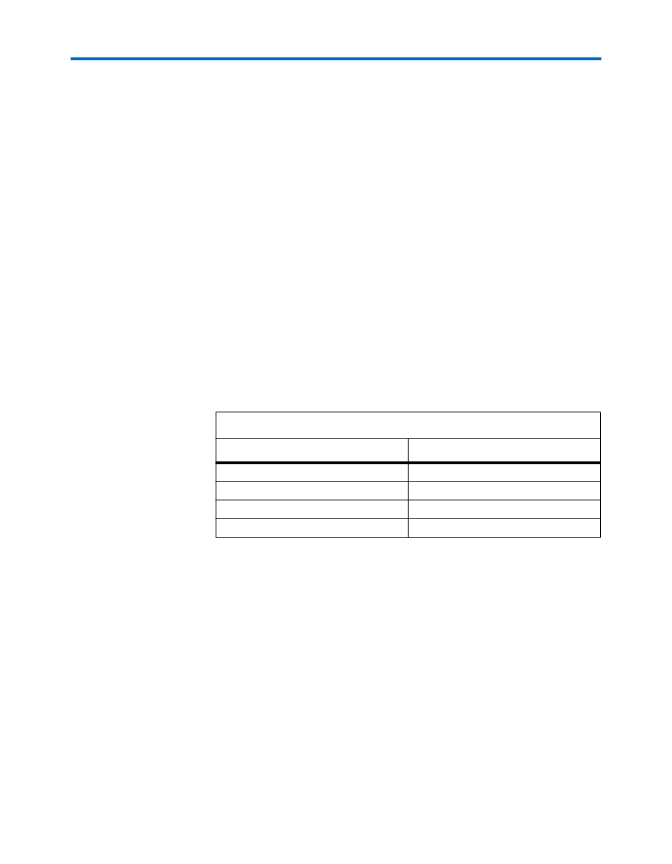

�Table� 4–4.� I/O� Pin� &� Resource� State�

�LED4/LED3�

�00�

�01�

�10�

�11�

�Number� of� I/O� Pins�

�16�

�32�

�48�

�64�

�Similarly,� the� toggle-frequency� of� these� I/O� pins� is� set� by� the� overall�

�design� frequency� (refer� to� Table� 4–1� ).�

�Changing� the� Example� Design�

�The� source� code� for� the� Cyclone� III� power� example� design� is� also�

�provided� so� you� can� use� it� as� a� starting� point� for� your� own� measurements.�

�You� can� adjust� the� number� of� outputs� by� changing� parameter�

�NUM_OUTPUTS_PER_STAMP� .� The� default� is� 16,� which� for� four� resource�

�percentage� steps� equates� to� 16� x� 4� =� 64.�

�The� appropriate� pins� to� be� used� as� outputs� are� pre-assigned� to� the� HSMC�

�connector� (J1).� If� you� would� like� to� look� at� more� than� the� 76� I/Os� available�

�on� J1,� you� need� to� make� the� appropriate� pin� assignments.�

�Altera� Corporation�

�4–3�

�July� 2010�

�Cyclone� III� FPGA� Starter� Kit� User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| DK-NIOS-2C35N | NIOS II KIT W/CYCLONE II EP2C35N |

| DK-NIOS-2S60N | NIOS II KIT W/STRATIX II EP2S60N |

| DK-PCI-2C35N | PCI KIT W/CYCLONE II EP2C35N |

| DK-PCIE-2SGX90N | PCIE KIT W/S II GX EP2SGX90N |

| DK-SI-2SGX90N | SI KIT W/SII GX EP2SGX90N |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-N2EVAL-3C25N/QP | 制造商:Altera Corporation 功能描述: |

| DK-N2EVAL-3C25N-OJ | 制造商:Altera 功能描述:DK-N2EVAL-3C25N-OJ |

| DK-N55224 | 制造商:Brother 功能描述: |

| DKN7900P-4-AA-1 | 制造商:DEUTSCH FAST / HUCK 功能描述: |

| DKNIL12VF | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:10 A MINIATURE POWER RELAY |

发布紧急采购,3分钟左右您将得到回复。