参数资料

| 型号: | DLP-USB245R |

| 厂商: | DLP Design Inc |

| 文件页数: | 7/13页 |

| 文件大小: | 0K |

| 描述: | MODULE USB-TO-PARL FIFO 18-DIP |

| 产品目录绘图: | DLP-USB2(32, 45)R |

| 标准包装: | 1 |

| 类型: | USB 至 FIFO |

| 连接器类型: | 迷你型 B 至 DIL(双直插式) |

| 产品目录页面: | 635 (CN2011-ZH PDF) |

| 其它名称: | 813-1025 |

�� �

�

�

�PI N #�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�16�

�17�

�18�

�D� E� S� C� R� I� P� T� I� O� N�

�GROUND�

�DB2� -� FIFO� Data� Bus� Bit� 2�

�DB7� -� FIFO� Data� Bus� Bit� 7�

�DB5� -� FIFO� Data� Bus� Bit� 5�

�DB3� -� FIFO� Data� Bus� Bit� 3�

�PWREN#� -� Goes� low� after� the� module� is� configured� by� USB,� then� high� during� USB�

�Suspend.� This� output� can� be� used� to� control� an� external� P-channel,� logic-level� MOSFET�

�switch.� Enable� the� interface� pull-down� option� when� using� the� PWREN#� pin� in� this� way.�

�PWREN#� should� be� pulled� to� VCCIO� with� 10k-Ohm� resistor.�

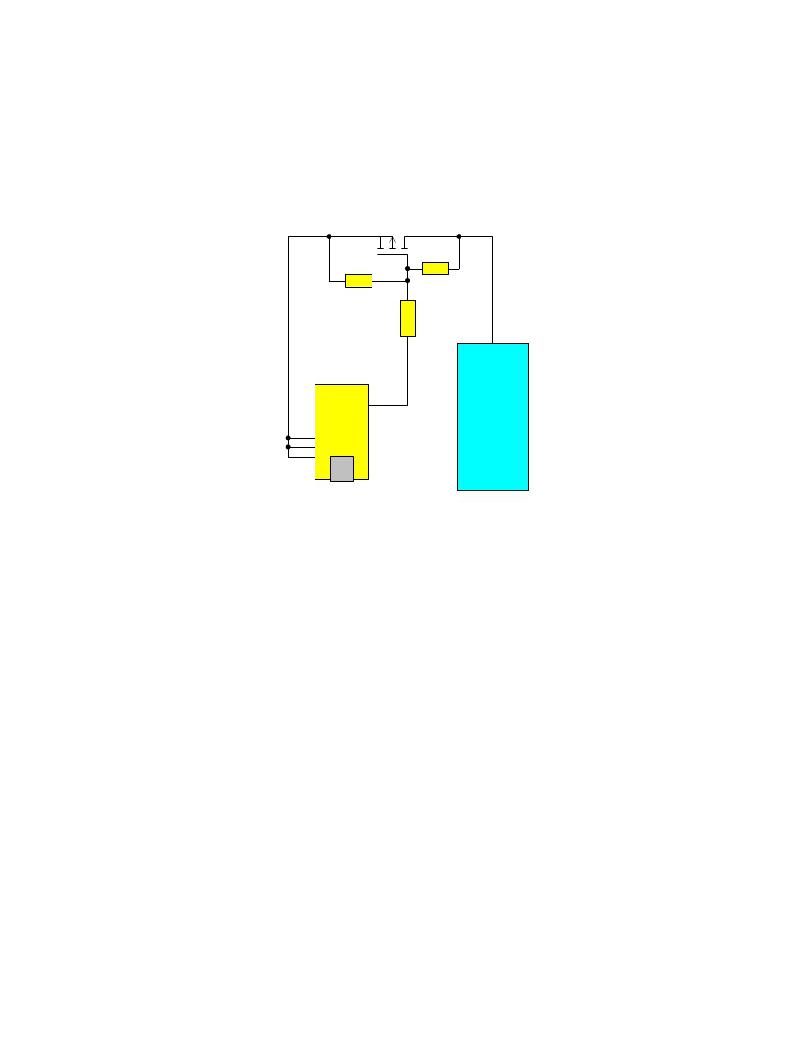

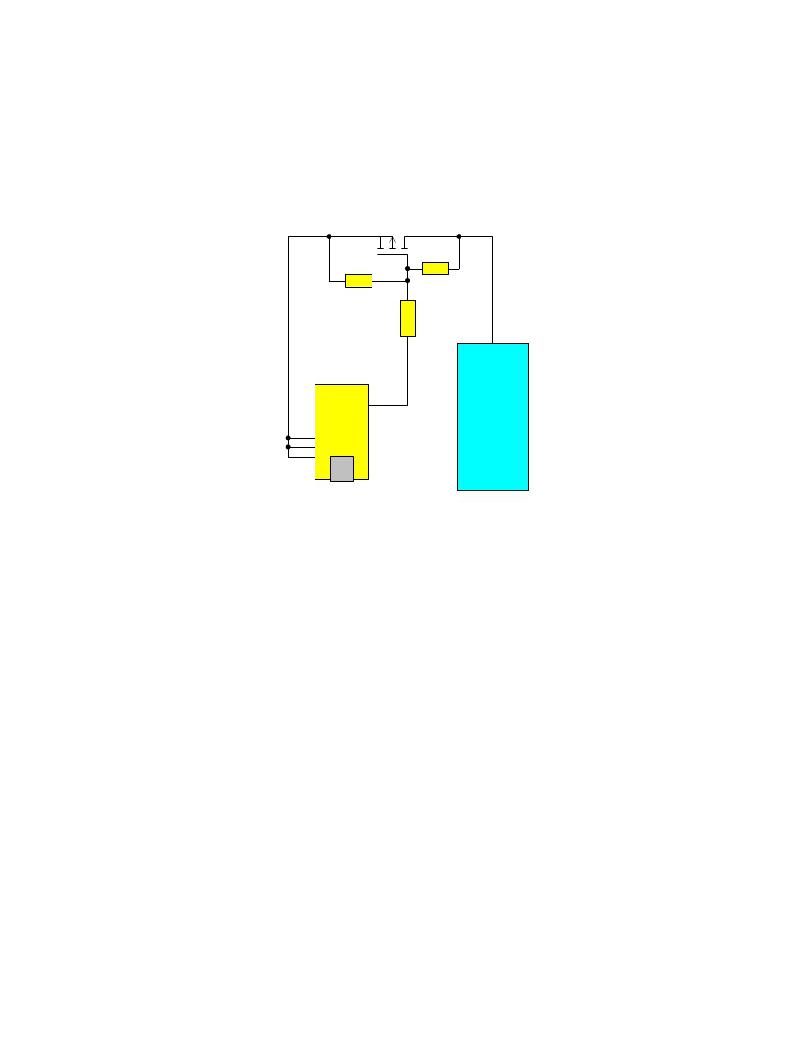

�VCCIO� -� +1.8V� to� +5.25V� supply� for� the� FIFO� interface.� Connect� this� pin� to� an� external�

�power� supply� to� drive� out� at� +3.3V� levels� (or� another� voltage� within� the� specified� range),�

�or� connect� to� EXTVCC� (Pin� 8)� to� drive� out� at� the� +5V� CMOS� level.�

�EXTVCC� -� Use� for� applying� main� power� (4.0� to� 5.25� volts)� to� the� module.� Connect� to�

�PORTVCC� (Pin� 9)� if� the� module� is� to� be� powered� by� the� USB� port� (typical� configuration).�

�PORTVCC� -� Power� from� the� USB� port.� Connect� to� EXTVCC� (Pin� 8)� if� the� module� is� to�

�be� powered� by� the� USB� port� (typical� configuration).� 500mA� is� the� maximum� current�

�available� to� the� USB� adapter� and� target� electronics� if� the� USB� device� is� configured� for�

�high� power.�

�GROUND�

�RD#� -� When� pulled� low,� RD#� takes� the� 8� data� lines� from� a� high-impedance� state� to� the�

�current� byte� in� the� FIFO’s� buffer.� Taking� RD#� high� returns� the� data� pins� to� a� high-�

�impedance� state� and� prepares� the� next� byte� (if� available)� in� the� FIFO� to� be� read.�

�WR� -� When� taken� from� a� high� to� a� low� state,� WR� reads� the� 8� data� lines� and� writes� the�

�byte� into� the� FIFO’s� transmit� buffer.� Data� written� to� the� transmit� buffer� is� sent� to� the� host�

�PC� within� the� TX� buffer� timeout� value� (default� 16mS)� and� placed� in� the� buffer� that� was�

�created� when� the� USB� port� was� opened.� The� FT245R� allows� the� TX� buffer� timeout� value�

�to� be� reprogrammed� to� a� value� between� 1� and� 255mS.�

�DB6� -� FIFO� Data� Bus� Bit� 6�

�TXE#� -� When� high,� do� not� write� data� into� the� FIFO.� When� low,� data� can� be� written� into�

�the� FIFO� by� strobing� WR� high,� then� low.� During� reset� this� signal� pin� is� tri-state.� Data� is�

�latched� into� the� FIFO� on� the� falling� edge� of� the� WR� pin.�

�RXF#� -� When� low,� at� least� 1� byte� is� present� in� the� FIFO’s� receive� buffer� and� is� ready� to�

�be� read� with� RD#.� RXF#� goes� high� when� the� receive� buffer� is� empty.� During� reset� this�

�signal� pin� is� tri-state.� If� the� Remote� Wakeup� option� is� enabled� in� the� internal� EEPROM,�

�during� USB� Suspend� Mode� (PWREN#=1)� RXF#� becomes� an� input.� This� can� be� used� to�

�wake� up� the� USB� host� from� Suspend� Mode� by� strobing� this� pin� low� for� a� minimum� of�

�20ms� which� will� cause� the� device� to� request� a� resume� on� the� USB� bus.�

�DB1� -� FIFO� Data� Bus� Bit� 1�

�DB4� -� FIFO� Data� Bus� Bit� 4�

�DB0� -� FIFO� Data� Bus� Bit� 0�

�Rev.� 1.0� (November� 2008)�

�7�

�?� DLP� Design,� Inc.�

�相关PDF资料 |

PDF描述 |

|---|---|

| DM163001 | BOARD DEMO PICDEM-1 |

| DM163004-LT | BOARD DEMO PICDEM.NET |

| DM163005 | KIT EVAL PIC16C432/433 LIN BUSS |

| DM163007 | PICDEM CAN-LIN 1 FOR 18C658/858 |

| DM163008 | KIT MCP2120/2150 FOR IRDA COMM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DLP-UT1 | 功能描述:工业温度传感器 TEMPERATURE SENSOR RoHS:否 制造商:Texas Instruments 准确性:1 C 功能:Temperature Sensing 25 摄氏度时的电阻: 温度范围:- 55 C to + 127 C 电源电流: 电源电压:2.7 V to 5.5 V |

| DLP-UTH8 | 功能描述:数据记录与采集 DLP SENSOR HUB RoHS:否 制造商:Lantronix 描述/功能:Analog device server 显示器类型:None 电流额定值: |

| DLPVA-100-F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Low Frequency Voltage Amplifier |

| DLPVA-100-F-D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Low Frequency Voltage Amplifier |

| DLPVA-100-F-S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Low Frequency Voltage Amplifier |

发布紧急采购,3分钟左右您将得到回复。