- 您现在的位置:买卖IC网 > PDF目录9168 > DS1807S+T&R (Maxim Integrated Products)IC POT ADDRESS 2X AUDIO 16-SOIC PDF资料下载

参数资料

| 型号: | DS1807S+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 9/13页 |

| 文件大小: | 0K |

| 描述: | IC POT ADDRESS 2X AUDIO 16-SOIC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1,000 |

| 接片: | 64 |

| 电阻(欧姆): | 45k |

| 电路数: | 2 |

| 温度系数: | 标准值 750 ppm/°C |

| 存储器类型: | 易失 |

| 接口: | I²C(芯片选择) |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC W |

| 包装: | 带卷 (TR) |

DS1807

5 of 13

110499

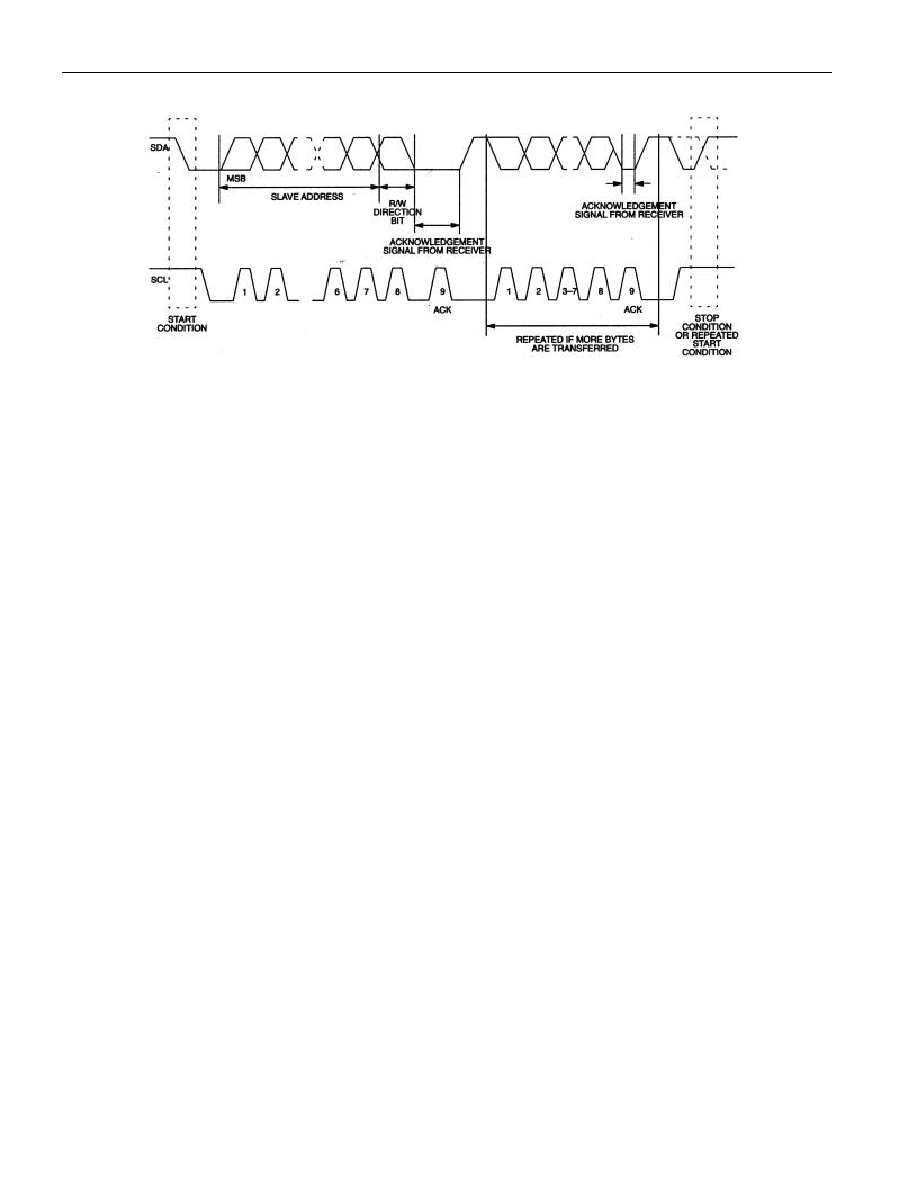

2-WIRE DATA TRANSFER OVERVIEW Figure 4

Accordingly, the following bus conditions have been defined:

Bus not busy: Both data and clock lines remain HIGH.

Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is

HIGH, defines a START condition.

Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is

HIGH, defines the STOP condition.

Data valid: The state of the data line represents valid data when, after a START condition, the data line

is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed

during the LOW period of the clock signal. There is one clock pulse per bit of data. Figure 4 details how

data transfer is accomplished on the 2-wire bus. Depending upon the state of the R/W bit, two types of

data transfer are possible:

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between START and STOP conditions is not limited, and is determined

by the master device. The information is transferred byte-wise and each receiver acknowledges with a 9th

bit.

Within the bus specifications a regular mode (100 kHz clock rate) and a fast mode (400 kHz clock rate)

are defined. The DS1807 works in both modes.

Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the

reception of each byte. The master device must generate an extra clock pulse which is associated with this

acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of

course, setup and hold times must be taken into account. A master must signal an end of data to the slave

by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable the master to generate the STOP condition.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-2WP-MY-F4 | CONVERTER MOD DC/DC 13.8V 50W |

| MS3450W24-5P | CONN RCPT 16POS WALL MNT W/PINS |

| V110A3V3H200B2 | CONVERTER MOD DC/DC 3.3V 200W |

| MS3450L24-5PZ | CONN RCPT 16POS WALL MNT W/PINS |

| VI-BWL-MV | CONVERTER MOD DC/DC 28V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS1808 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:Dual Log Digital Potentiometer |

| DS1808Z-050 | 功能描述:数字电位计 IC RoHS:否 制造商:Maxim Integrated 电阻:200 Ohms 温度系数:35 PPM / C 容差:25 % POT 数量:Dual 每 POT 分接头:256 弧刷存储器:Volatile 缓冲刷: 数字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作电源电压:1.7 V to 5.5 V 电源电流:27 uA 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:TQFN-16 封装:Reel |

| DS1808Z-050/T&R | 制造商:Maxim Integrated Products 功能描述:DUAL LOG HI VOLTAGE POT T&R - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC POT DUAL LOG HV 50K 16-SOIC |

| DS1808Z-050/T&R | 功能描述:数字电位计 IC RoHS:否 制造商:Maxim Integrated 电阻:200 Ohms 温度系数:35 PPM / C 容差:25 % POT 数量:Dual 每 POT 分接头:256 弧刷存储器:Volatile 缓冲刷: 数字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作电源电压:1.7 V to 5.5 V 电源电流:27 uA 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:TQFN-16 封装:Reel |

| DS1808Z-050+ | 功能描述:数字电位计 IC Dual Log RoHS:否 制造商:Maxim Integrated 电阻:200 Ohms 温度系数:35 PPM / C 容差:25 % POT 数量:Dual 每 POT 分接头:256 弧刷存储器:Volatile 缓冲刷: 数字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作电源电压:1.7 V to 5.5 V 电源电流:27 uA 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:TQFN-16 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。