- 您现在的位置:买卖IC网 > PDF目录9762 > DS21348GN+ (Maxim Integrated Products)IC LIU T1/E1/J1 3.3V 49-BGA PDF资料下载

参数资料

| 型号: | DS21348GN+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 30/76页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/E1/J1 3.3V 49-BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 416 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 1/1 |

| 规程: | T1/E1/J1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 49-LFBGA,CSPBGA |

| 供应商设备封装: | 49-CSBGA(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

DS21348/DS21Q348

36 of 76

5. STATUS REGISTERS

There are three registers that contain information on the current real-time status of the device, Status

Register (SR) and Receive Information Registers 1 and 2 (RIR1/RIR2). When a particular event has

occurred (or is occurring), the appropriate bit in one of these three registers will be set to a one. Some of

the bits in SR, RIR1, and RIR2 are latched bits and some are real time bits. The register descriptions

below list which status bits are latched and which are real time bits. For latched status bits, when an event

or an alarm occurs the bit is set to a one and will remain set until the user reads that bit. The bit will be

cleared when it is read and it will not be set again until the event has occurred again. Two of the latched

status bits (RUA1 and RCL) will remain set after reading if the alarm is still present.

The user will always precede a read of any of the three status registers with a write. The byte written to

the register will inform the DS21348 which bits the user wishes to read and have cleared. The user will

write a byte to one of these registers with a one in the bit positions to be read and a zero in the other bit

positions. When a one is written to a bit location, that location will be updated with the latest information.

When a zero is written to a bit position, that bit position will not be updated and the previous value will

be held. A write to the status and information registers will be immediately followed by a read of the

same register. The read result should be logically ANDed with the mask byte that was just written and

this value should be written back into the same register to insure that bit does indeed clear. This second

write step is necessary because the alarms and events in the status registers occur asynchronously with

respect to their access via the parallel port. This write-read-write scheme allows an external

microcontroller or microprocessor to individually poll certain bits without disturbing the other bits in the

register. This operation is key in controlling the DS21348 with higher-order software languages.

The bits in the SR register have the unique ability to initiate a hardware interrupt via the

INT output pin.

Each of the alarms and events in the SR can be either masked or unmasked from the interrupt pin via the

Interrupt Mask Register (IMR). The interrupts caused by the RCL, RUA1, and LOTC bits in SR act

differently than the interrupts caused by the other status bits in SR. The RCL, RUA1 and LOTC bits will

force the

INT pin low whenever they change state (i.e., go active or inactive). The INT pin will be

allowed to return high (if no other interrupts are present) when the user reads the alarm bit that caused the

interrupt to occur even if the alarm is still present. The other status bits in SR can force the

INT pin low

when they are set. The

INT pin will be allowed to return high (if no other interrupts are present) when the

user reads the event bit that caused the interrupt to occur.

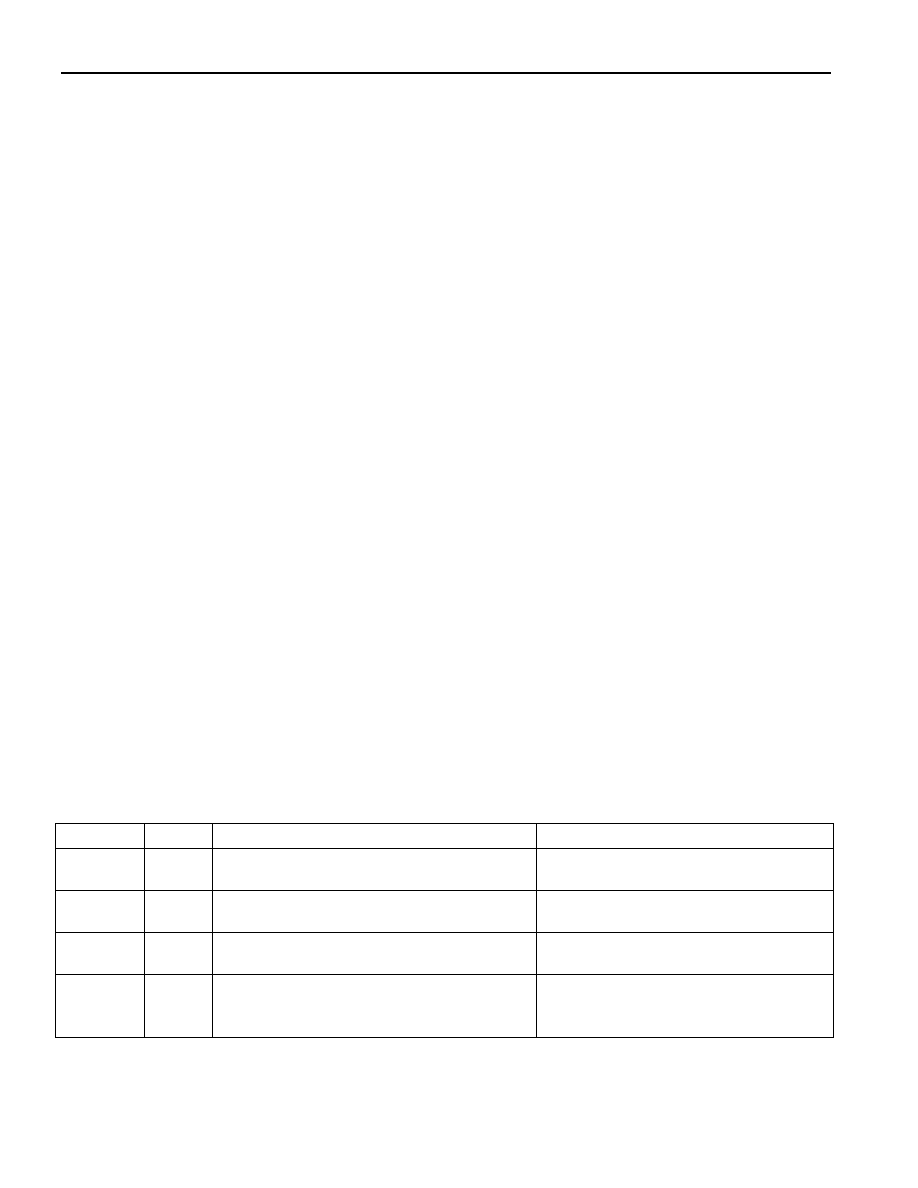

Table 5-1. Received Alarm Criteria

ALARM

E1/T1

SET CRITERIA

CLEAR CRITERIA

RUA1

E1

Less than 2 zeros in two frames (512 bits)

More than 2 zeros in two frames (512

bits)

RUA1

T1

Over a 3ms window, five or fewer zeros

are received

Over a 3ms window, six or more zeros

are received

RCL1

E1

255 (or 2048)2 consecutive zeros received

(G.775)

In 255 bit times, at least 32 ones are

received

RCL1

T1

192 (or 1544)2 consecutive zeros are

received

14 or more ones out of 112 possible

bit positions are received starting with

the first one received

Note 1:

Receive carrier loss (RCL) is also known as loss of signal (LOS) or Red Alarm in T1.

Note 2:

See CCR1.5 for details.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3122E12-10SW | CONN RCPT 10POS BOX MNT W/SCKT |

| MS3106R-24-10P | CONN PLUG 7POS STRAIGHT W/PINS |

| MS27468T23F35SA | CONN RCPT 100POS JAM NUT W/SCKT |

| MS3102R36-7P | CONN RCPT 47POS BOX MNT W/PINS |

| MS27468E23F35SA | CONN RCPT 100POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS21348GN+ | 功能描述:网络控制器与处理器 IC 3.3V E1/T1/J1 Line Interface RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21348GNB | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21348GN-C01 | 功能描述:网络控制器与处理器 IC 3.3V E1/T1/J1 Line Interface RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21348T | 功能描述:网络控制器与处理器 IC 3.3V E1/T1/J1 Line Interface RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21348T+ | 功能描述:网络控制器与处理器 IC 3.3V E1/T1/J1 Line Interface RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。