- 您现在的位置:买卖IC网 > PDF目录97866 > DS2141A (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PDIP40 PDF资料下载

参数资料

| 型号: | DS2141A |

| 厂商: | DALLAS SEMICONDUCTOR |

| 元件分类: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PDIP40 |

| 封装: | 0.600 INCH, DIP-40 |

| 文件页数: | 34/39页 |

| 文件大小: | 470K |

| 代理商: | DS2141A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页

DS2141A

4 of 39

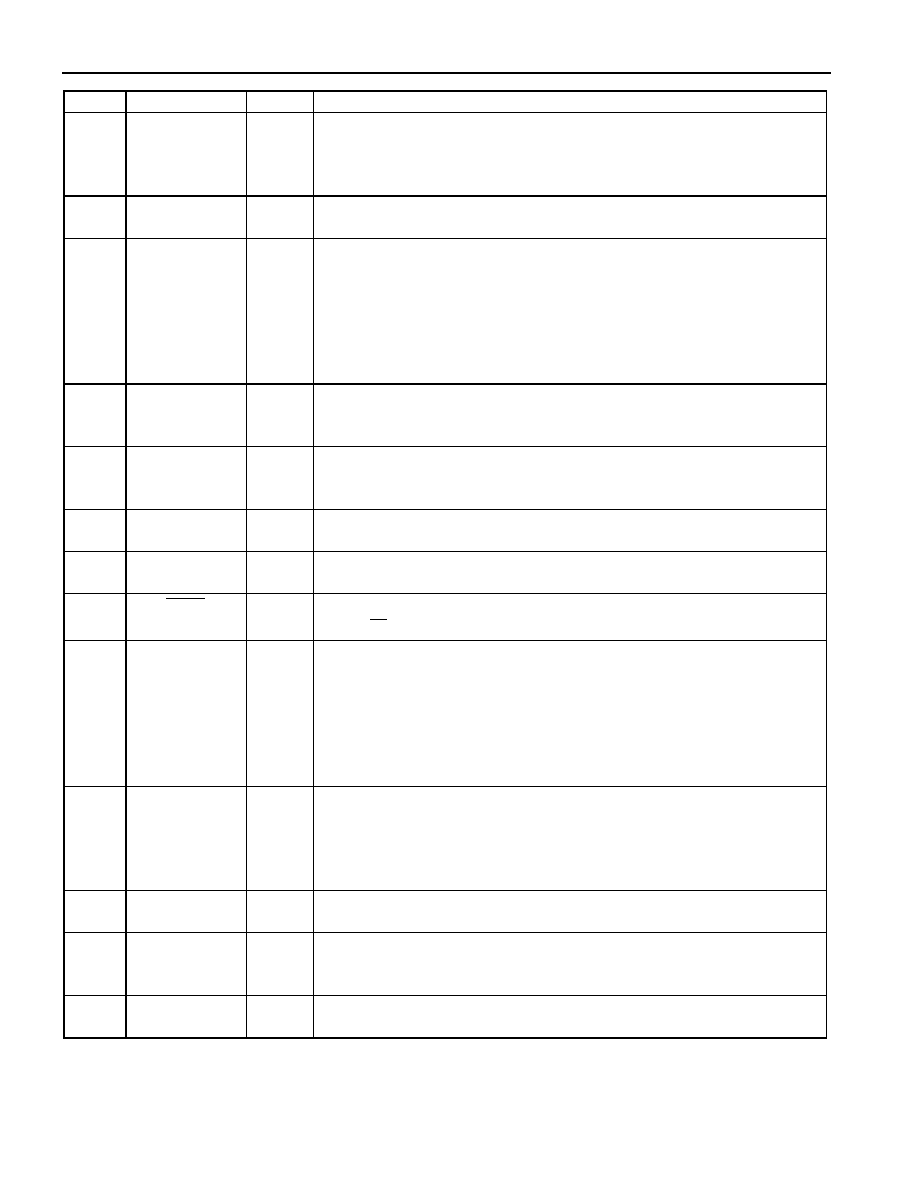

PIN

SYMBOL

TYPE

DESCRIPTION

23

RCHCLK

O

Receive Channel Clock. 192 kHz clock which pulses high during

the LSB of each channel. Useful for parallel-to-serial conversion of

channel data, locating robbed-bit signaling bits, and for blocking

clocks in DDS applications. See Section 13 for timing details.

24

RSER

O

Receive Serial Data. Received NRZ serial data; updated on rising

edges of RCLK.

25

RSYNC

I/O

Receive Sync. An extracted pulse, one RCLK wide, is output at this

pin which identifies either frame (RCR2.4=0) or multiframe

boundaries (RCR2.4=1). If set to output frame boundaries, then via

RCR2.5, RSYNC can also be set to output double-wide pulses on

signaling frames. If the elastic store is enabled via the CCR1.2, then

this pin can be enabled to be an input via RCR2.3 at which a frame

boundary pulse is applied. See Section 13 for timing details.

26

27

RPOS

RNEG

I

Receive Bipolar Data Inputs. Sampled on falling edge of RCLK.

Tie together to receive NRZ data and disable bipolar violation

monitoring circuitry.

28

SYSCLK

I

System Clock. 1.544 MHz or 2.048 MHz clock. Only used when

the elastic store function is enabled via the CCR. Should be tied low

in applications that do not use the elastic store.

29

LI_SDI

O

Serial Port Data for the Line Interface. Connects directly to the

SDI input pin on the line interface.

30

LI_CLK

O

Serial Port Clock for the Line Interface. Connects directly to the

SCLK input pin on the line interface.

31

LI_CS

O

Serial Port Chip Select for the Line Interface. Connects directly

to the CS input pin on the line interface.

32

33

RCHBLK

TCHBLK

O

Receive/Transmit Channel Block. A user-programmable output

that can be forced high or low during any of the 24 T1 channels.

Useful for blocking clocks to a serial UART or LAPD controller in

application where not all T1 channels are used such as Fractional

T1, 384K bps service, 768K bps, or ISDN-PRI. Also useful for

locating individual channels in drop-and-insert applications. See

Section 13 for timing details.

34

RLOS/LOTC

O

Receive Loss of Sync/Loss of Transmit Clock. A dual function

output. If CCR1.6=0, then this pin will toggle high when the

synchronizer is searching for the T1 frame and multiframe. If

CCR1.6=1, then this pin will toggle high when the TCLK pin has

not been toggled for 5 ms.

35

INT2

O

Receive Alarm Interrupt 2. Flags host controller during conditions

defined in Status Register 2. Active low, open drain output.

36

INT1

O

Receive Alarm Interrupt 1. Flags host controller during alarm

conditions defined in Status Register 1. Active low, open drain

output.

37

TLCLK

O

Transmit Link Clock. 4 kHz or 2 kHz (ZBTSI) demand clock for

the TLINK input. See Section 13 for timing details.

相关PDF资料 |

PDF描述 |

|---|---|

| DS2143N | DATACOM, FRAMER, PDIP40 |

| DS2143QN | DATACOM, FRAMER, PQCC44 |

| DS2143Q | DATACOM, FRAMER, PQCC44 |

| DS2143 | DATACOM, FRAMER, PDIP40 |

| DS2148GN | DATACOM, PCM TRANSCEIVER, BGA49 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2141AN | 功能描述:网络控制器与处理器 IC T1 Controller w/Elastic Store RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2141AQ | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2141AQ/T&R | 制造商:Maxim Integrated Products 功能描述:T1 CONTROL. W/ELAS.ST. 44-PLCC TRL - Tape and Reel 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述:IC CONTROLLER T1 5V 44-PLCC |

| DS2141AQ/T&R+ | 制造商:Maxim Integrated Products 功能描述:T1 CNTRLR 44PLCC - Tape and Reel |

| DS2141AQ/T&R | 功能描述:网络控制器与处理器 IC T1 Controller w/Elastic Store RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。