- 您现在的位置:买卖IC网 > PDF目录1994 > DS2404B (Maxim Integrated Products)IC ECONORAM TIMECHIP 5.5V 16SSOP PDF资料下载

参数资料

| 型号: | DS2404B |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 5/29页 |

| 文件大小: | 0K |

| 描述: | IC ECONORAM TIMECHIP 5.5V 16SSOP |

| 标准包装: | 77 |

| 系列: | EconoRAM |

| 类型: | 二进制计数器 |

| 特点: | 警报器,方波输出 |

| 时间格式: | 二进制 |

| 数据格式: | 二进制 |

| 接口: | 1 线和 3 线 |

| 电源电压: | 2.8 V ~ 5.5 V |

| 电压 - 电源,电池: | 2.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 16-SSOP |

| 包装: | 管件 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

DS2404

13 of 29

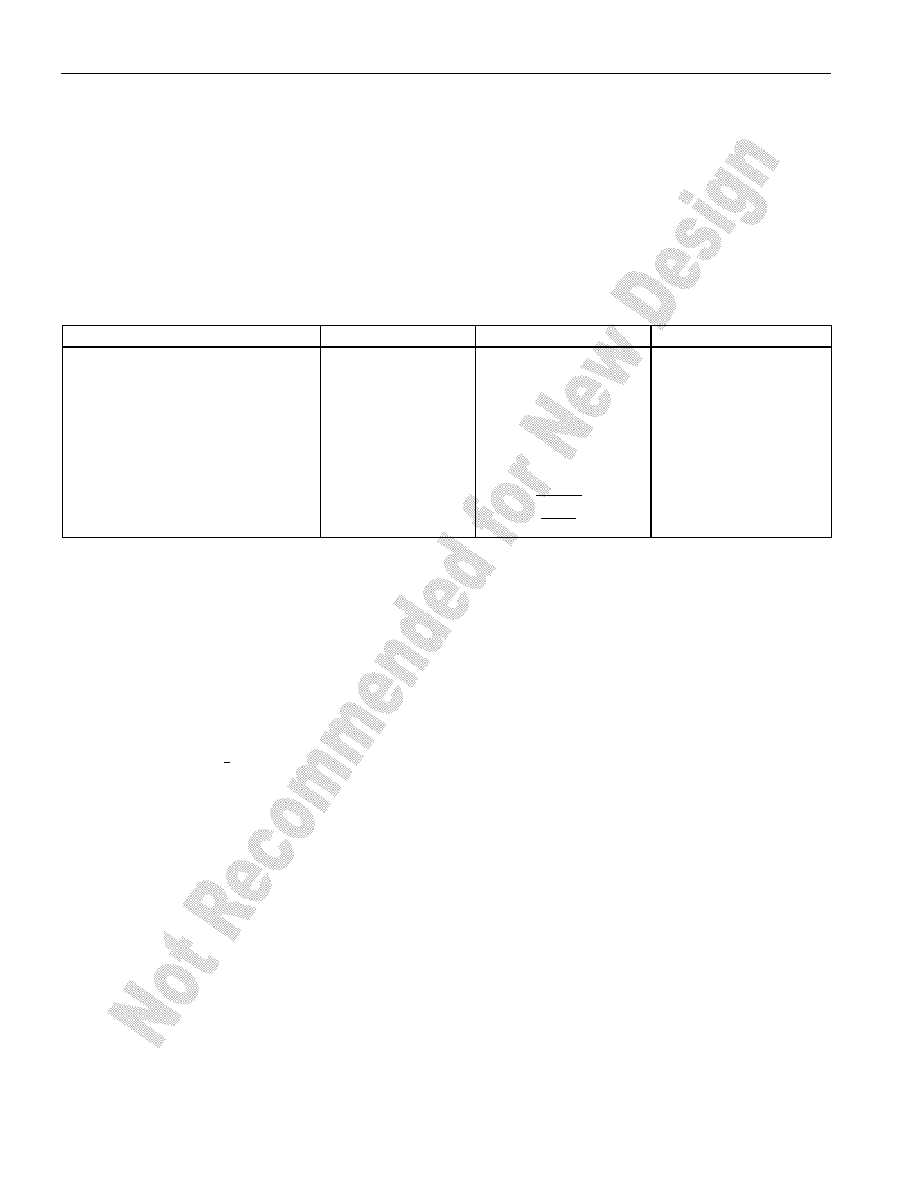

The write protect bits, once set, permanently write protects their corresponding counter and alarm

registers, all write protect bits, and certain control register bits as shown in Figure 7. The time/count

registers will continue to count if the oscillator is enabled. If the user wishes to set more than one write

protect bit, the user must set them at the same time. Once a write protect bit is set it cannot be undone,

and the remaining write protect bits, if not set, cannot be set.

The programmable expiration takes place when one or more write protect bits have been set and a

corresponding alarm occurs. If the RO (read only) bit is set, only the read scratchpad and read memory

function commands are available. If the RO bit is a logic “0”, no memory function commands are

available. The ROM functions are always available.

WRITE PROTECT CHART Figure 7

WRITE PROTECT BIT SET:

WPR

WPI

WPC

Data Protected from

User Modification:

Real Time Clock

Real Time Alarm

WPR

WPI

WPC

RO

OSC *

Interval Timer

Interval Time Alarm

WPR

WPI

WPC

RO

OSC *

STOP/ START **

AUTO/ MAN

Cycle Counter

Cycle Counter Alarm

WPR

WPI

WPC

RO

OSC *

DSEL

* Becomes write “1” only, i.e., once written to a logic “1”, may not be written back to a logic “0”.

** Forced to a logic “0”.

1-WIRE BUS SYSTEM

The 1-Wire bus is a system which has a single bus master and one or more slaves. In most instances the

DS2404 behaves as a slave. The exception is when the DS2404 generates an interrupt due to a

timekeeping alarm. The discussion of this bus system is broken down into three topics: hardware

configuration, transaction sequence, and 1-Wire signaling (signal types and timing). The 1-Wire protocol

defines bus transactions in terms of the bus state during specific time slots that are initiated on the falling

edge of sync pulses from the bus master. For a more detailed protocol description, refer to Chapter 4 of

the Book of DS19XX iButton Standards.

HARDWARE CONFIGURATION

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to

drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open

drain or 3-state outputs. The 1-Wire port of the DS2404 (I/O pin 5) is open drain with an internal circuit

equivalent to that shown in Figure 8. A multidrop bus consists of a 1-Wire bus with multiple slaves

attached. The 1-Wire bus has a maximum data rate of 16.3k bits per seconds. Depending on 1-Wire

communication speed and bus load characteristics, the optimal pull-up resistor value will be in the 1.5 k

Ω

to 5 k

Ω range.

The idle state for the 1-Wire bus is high. If for any reason a transaction needs to be suspended, the bus

MUST be left in the idle state if the transaction is to resume. If this does not occur and the bus is left low

for more than 120

μs, one or more of the devices on the bus may be reset.

相关PDF资料 |

PDF描述 |

|---|---|

| DS2415P+T&R | IC TIME CHIP 1-WIRE 6-TSOC |

| DS2417X/T&R | IC TIMECHIP W/INTRPT 1WIRE CSP |

| DS26502LN+ | IC T1/E1/J1 64KCC ELEMENT 64LQFP |

| DS26503LN+ | IC T1/E1/J1 BITS ELEMENT 64-LQFP |

| DS3105LN+ | IC TIMING LINE CARD 64-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2404B/T&R | 制造商:Maxim Integrated Products 功能描述:ECONORAM/TIME, SSOP16-TRL (GENERIC) - Tape and Reel |

| DS2404B+ | 制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 512BYTE 16SSOP - Rail/Tube |

| DS2404B+T&R | 制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 512BYTE 16SSOP - Tape and Reel |

| DS2404FP000 | 制造商:Thomas & Betts 功能描述:200A,CON,3P4W,MG,404,3P480V |

| DS2404FP000/DF2029 | 制造商:Thomas & Betts 功能描述:RS DS2404FP000/DF2029 200A,CON,3P4W |

发布紧急采购,3分钟左右您将得到回复。