- 您现在的位置:买卖IC网 > PDF目录9748 > DS32512N (Maxim Integrated Products)IC 12CH DS3/E3/STS1 LIU 484-BGA PDF资料下载

参数资料

| 型号: | DS32512N |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 73/130页 |

| 文件大小: | 0K |

| 描述: | IC 12CH DS3/E3/STS1 LIU 484-BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 类型: | 线路接口装置(LIU) |

| 规程: | DS3 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 484-BGA |

| 供应商设备封装: | 484-BGA(23x23) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页当前第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

DS32506/DS32508/DS32512

47 of 130

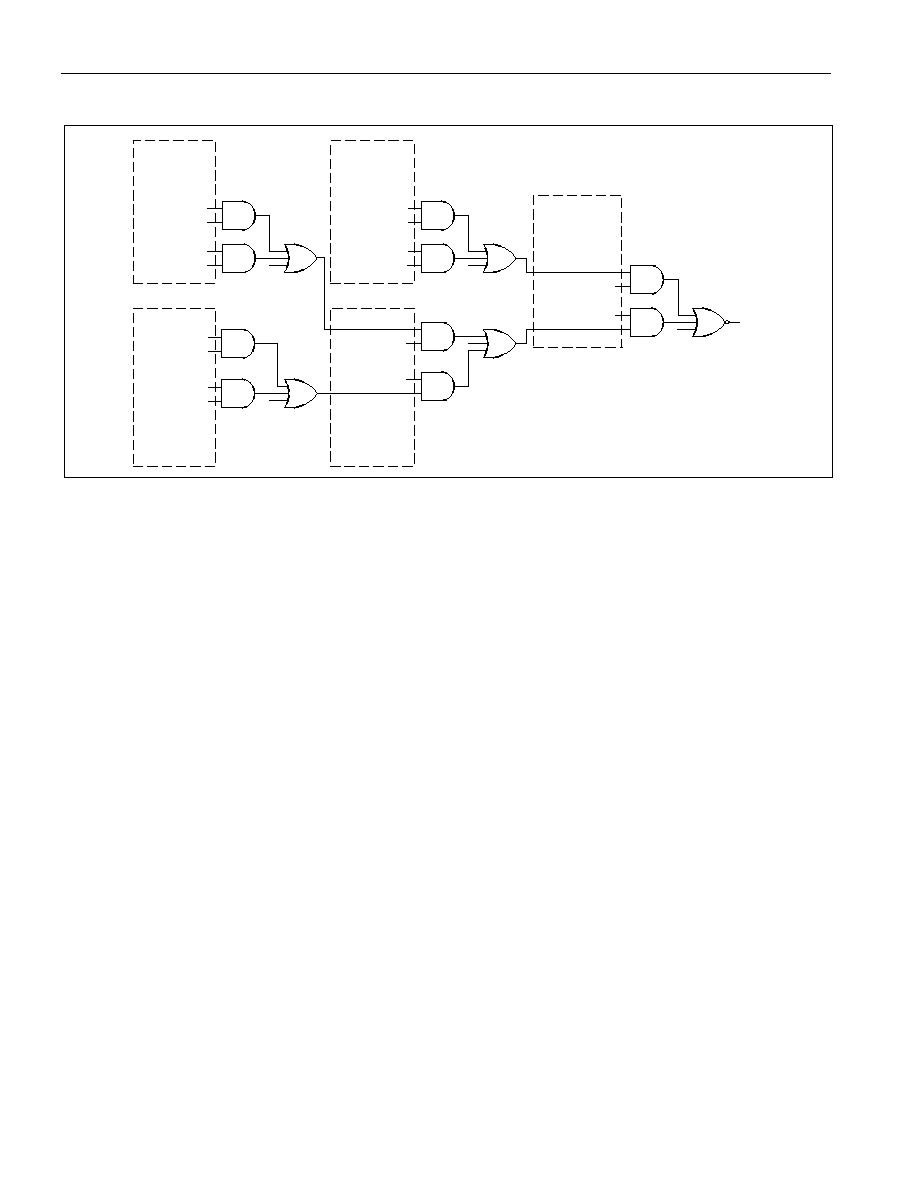

Figure 8-12. Interrupt Signal Flow

GLOBAL LATCHED

STATUS REGISTER

AND INTERRUPT

ENABLE REGISTER

INT*

GLOBAL.SRL bit

GLOBAL.SRIE bit

GLOBAL INTERRUPT

STATUS REGISTER

AND INTERRUPT

ENABLE REGISTER

GLOBAL.ISR bit

GLOBAL.ISRIE bit

BLOCK LATCHED

STATUS REGISTER

AND INTERRUPT

ENABLE REGISTER

block SRL bit

block SRIE bit

PORT INTERRUPT

STATUS REGISTER

AND INTERRUPT

ENABLE REGISTER

PORT.ISRIE bit

PORT.ISR bit

PORT.ISRIE bit

PORT.SRL bit

PORT LATCHED

STATUS REGISTER

AND INTERRUPT

ENABLE REGISTER

PORT.SRIE bit

PORT.SRL bit

PORT.SRIE bit

block SRL bit

block SRIE bit

GLOBAL.SRL bit

GLOBAL.SRIE bit

GLOBAL.ISRIE bit

GLOBAL.ISR bit

8.11 Reset and Power-Down

When only the hardware interface is enabled (IFSEL = 000 and HW = 1), the device is can be reset via the RST

pin. The transmitters of all ports can be powered down using the TPD pin, while the receivers of all ports can be

powered down using the RPD pin.

When a microprocessor interface is enabled (IFSEL

≠ 000), the device presents a number of reset and power down

options. The device can be reset at a global level via the GLOBAL.CR1:RST bit or the RST pin, and at the port

level via the PORT.CR1:RST bit. Each port can be powered down via the PORT.CR1:TPD and RPD bits. The

JTAG logic is reset by the

JTRST pin.

The external RST pin and the global reset bit (GLOBAL.CR1:RST) are combined to create an internal global reset

signal. The global reset signal resets all the status and control registers on the chip (except the GLOBAL.CR1:RST

bit), to their default values. It also resets all flip-flops in the global logic (including the CLAD block) and port logic to

their reset values. The GLOBAL.CR1:RST bit stays set after a one is written to it. It is reset to zero when a zero is

written to it or when the external RST pin is active.

At the port level, the global reset signal combines with the port reset bit (PORT.CR1:RST) to create a port reset

signal. The port reset signal resets all the status and control registers in the port (except PORT.CR1:RST bit) to

their default values. It also resets all flip-flops in the port logic to their reset values. The port reset bit

(PORT.CR1:RST) stays set after a one is written to it. It is reset to zero when a zero is written to it or when the

global reset signal is active.

The data path reset (RSTDP) resets all of the same registers and flip-flops as the “general” reset (RST), except for

the control registers. This allows the device to be programmed while the data path logic is in reset. It is

recommended that a port be placed in data path reset during configuration changes.

The global data path reset bit (GLOBAL.CR1:RSTDP) is set to one when the global reset signal is active. This bit is

cleared when a zero is written to it while the global reset signal is inactive. The global data path reset resets all of

the data path registers and flip-flops on the chip.

The port data path reset bit (PORT.CR1:RSTDP) is set to one when the port reset signal is active. It is cleared

when a zero is written to it while the port reset signal is inactive. The port data path reset resets all of the port logic

data path registers and flip-flops.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102E18-14S | CONN RCPT 2POS BOX MNT W/SCKT |

| DS32512N# | IC LIU DS3/E3/STS-1 484-BGA |

| MAX1228AEEP+T | IC ADC 12BIT 300KSPS 20-QSOP |

| VI-26W-IU-F4 | CONVERTER MOD DC/DC 5.5V 200W |

| DS32512+ | IC LIU DS3/E3/STS-1 484-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS32512N# | 功能描述:网络控制器与处理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS32512N+ | 功能描述:网络控制器与处理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS32512NA2 | 制造商:Maxim Integrated Products 功能描述:DS32512 X12 DS3/E3 LIU REVA2 IND - Rail/Tube |

| DS32512NW | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS32512W | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。