- 您现在的位置:买卖IC网 > PDF目录9178 > DS3930E+T&R (Maxim Integrated Products)IC POT NV HEX I/O MEM 20-TSSOP PDF资料下载

参数资料

| 型号: | DS3930E+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 12/12页 |

| 文件大小: | 0K |

| 描述: | IC POT NV HEX I/O MEM 20-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 接片: | 256 |

| 电阻(欧姆): | 16.5k |

| 电路数: | 6 |

| 温度系数: | 标准值 ±250 ppm/°C |

| 存储器类型: | 非易失 |

| 接口: | I²C(设备位址) |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 带卷 (TR) |

DS3930

Hex Nonvolatile Potentiometer with

I/O and Memory

_____________________________________________________________________

9

2-Wire Serial Port Operation

The 2-wire serial port interface supports a bidirectional

data transmission protocol with device addressing. A

device that sends data on the bus is defined as a trans-

mitter, and a device receiving data as a receiver. The

device that controls the message is called a “master.”

The devices that are controlled by the master are

“slaves.” The bus must be controlled by a master

device that generates the serial clock (SCL), controls

the bus access, and generates the start and stop con-

ditions. The DS3930 operates as a slave on the 2-wire

bus. Connections to the bus are made through the

open-drain I/O lines, SDA and SCL. The following I/O

terminals control the 2-wire serial port: SDA, SCL, and

A0. Timing diagrams for the 2-wire serial port can be

found in Figures 3 and 5. Timing information for the 2-

wire serial port is provided in the AC Electrical

Characteristics table for 2-wire serial communications.

The following bus protocol has been defined:

Data transfer can be initiated only when the bus is

not busy.

During data transfer, the data line must remain sta-

ble whenever the clock line is high. Changes in the

data line while the clock line is high are interpreted

as control signals.

Accordingly, the following bus conditions have been

defined:

Bus Not Busy: Both data and clock lines remain high.

Start Data Transfer: A change in the state of the data

line from high to low while the clock is high defines a

start condition.

Stop Data Transfer: A change in the state of the data

line from low to high while the clock line is high defines

the stop condition.

Data Valid: The state of the data line represents valid

data when, after a start condition, the data line is stable

for the duration of the high period of the clock signal. The

data on the line can be changed during the low period of

the clock signal. There is one clock pulse per bit of data.

Figures 3 and 5 detail how data transfer is accomplished

on the 2-wire bus. Depending upon the state of the R/W

bit, two types of data transfer are possible.

Each data transfer is initiated with a start condition and

STOP

CONDITION

OR REPEATED

START

CONDITION

REPEATED IF MORE BYTES

ARE TRANSFERRED

ACK

START

CONDITION

ACK

ACKNOWLEDGEMENT

SIGNAL FROM RECEIVER

ACKNOWLEDGEMENT

SIGNAL FROM RECEIVER

SLAVE ADDRESS

MSB

SCL

SDA

R/W

DIRECTION

BIT

12

6

7

8

9

12

8

9

3–7

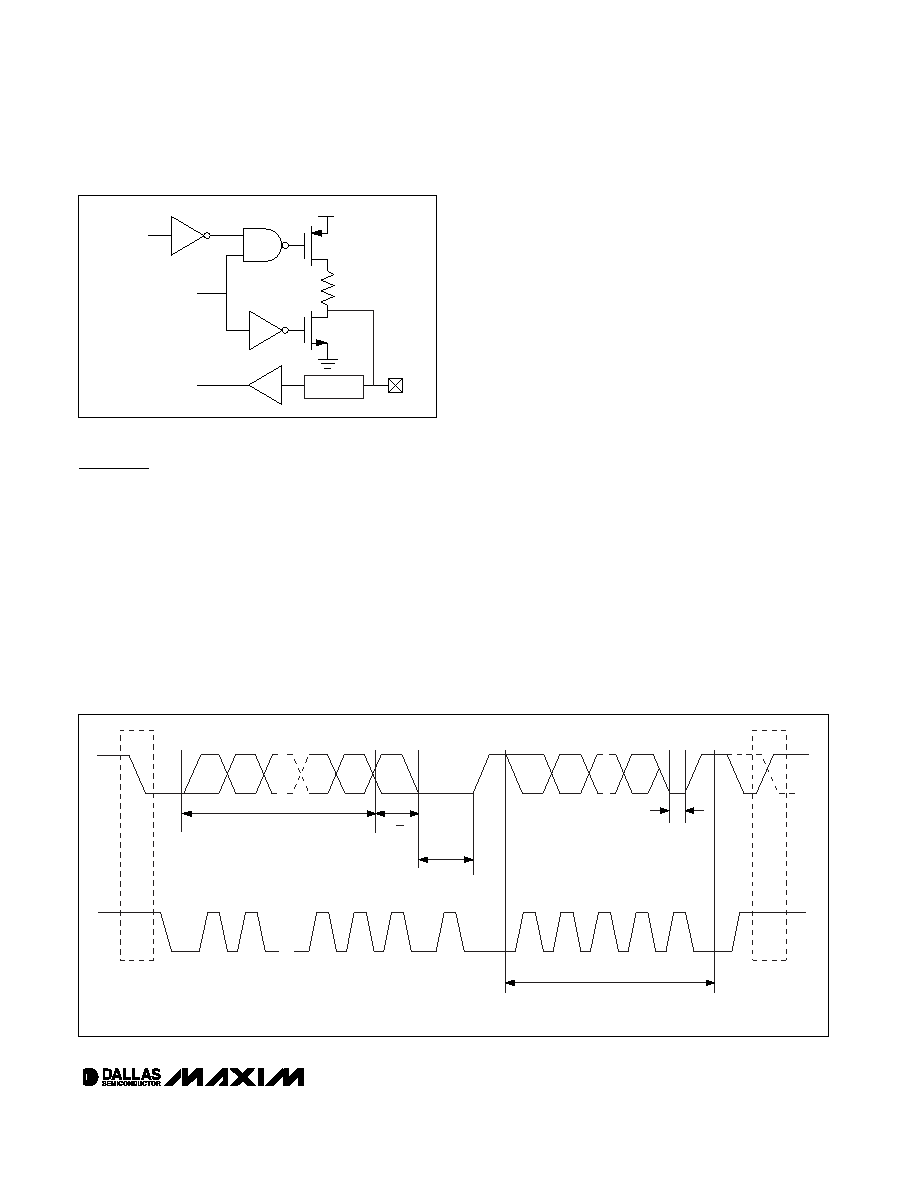

Figure 3. 2-Wire Data Transfer Protocol

PULLUP

CTRL

I/O PIN

SETTING

RI/O

VCC

ESD

I/O

INPUT

Figure 2. I/O Cell

相关PDF资料 |

PDF描述 |

|---|---|

| 7SB384DTT1G | 1 BIT DIGITAL SWITCH TSOP-5 |

| 7SB384DFT2G | 1 BIT DIGITAL SWITCH SC-88A |

| 7SB385DFT2G | 1 BIT DIGITAL SWITCH SC-88A |

| MAX5420BEUA+T | IC VOLTAGE DIVIDER DGLT 8-UMAX |

| 7SB3257AMX1TCG | 1 BIT MUX/DEMUX BUS SWTCH ULLGA6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3984 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4-Channel Cold-Cathode Fluorescent Lamp Controller |

| DS3984T | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4-Channel Cold-Cathode Fluorescent Lamp Controller |

| DS3984T+ | 功能描述:显示驱动器和控制器 RoHS:否 制造商:Panasonic Electronic Components 工作电源电压:2.7 V to 5.5 V 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Reel |

| DS3984Z | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4-Channel Cold-Cathode Fluorescent Lamp Controller |

| DS3984Z+ | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:4-Channel Cold-Cathode Fluorescent Lamp Controller |

发布紧急采购,3分钟左右您将得到回复。