- 您现在的位置:买卖IC网 > PDF目录97874 > ECOG1 eCOG1 Microcontroller PDF资料下载

参数资料

| 型号: | ECOG1 |

| 英文描述: | eCOG1 Microcontroller |

| 中文描述: | eCOG1微控制器 |

| 文件页数: | 1/11页 |

| 文件大小: | 277K |

| 代理商: | ECOG1 |

V3.1

www.cyantechnology.com

1-Mar-2002

The eCOG1 microcontroller is a low-power microcontroller based on a 16-bit Harvard architecture

with a 24-bit word code linear address space (32Mbyte) and 16-bit word linear data address

space (128Kbytes). It is available in a 128-pin LQFP with or without the IntAct high-speed serial

interface. A comprehensive toolset and C Compiler are available.

0 to 25MHz 3.3V processor

Powerful arithmetic operations

Barrel Shifter

Harvard Architecture

64Kx16 Data Memory

16Mx16 Program Memory

Built in Emulator (eICE)

Low power operation

64Kbytes FLASH EPROM

4Kbytes SRAM

MMU

Power-saving code cache

Code security feature

External Host Interface

External Memory Interface

Fast Vectored Interrupts

Dual UART

Dual USART

Smart Card Interface

SPI

I2C

Consumer IR/IRDA

4 channel 12-bit A/D

Parallel Interface

5 Multi Purpose Timers

Watchdog Timer

Long Interval Timer

Real Time Clock

PWM timers

Temperature Sensor

Supply Voltage Sensor

Power-On Reset

General Purpose I/O

25MHz from watch XTAL

Interfaces to 8/16/32-bit parts

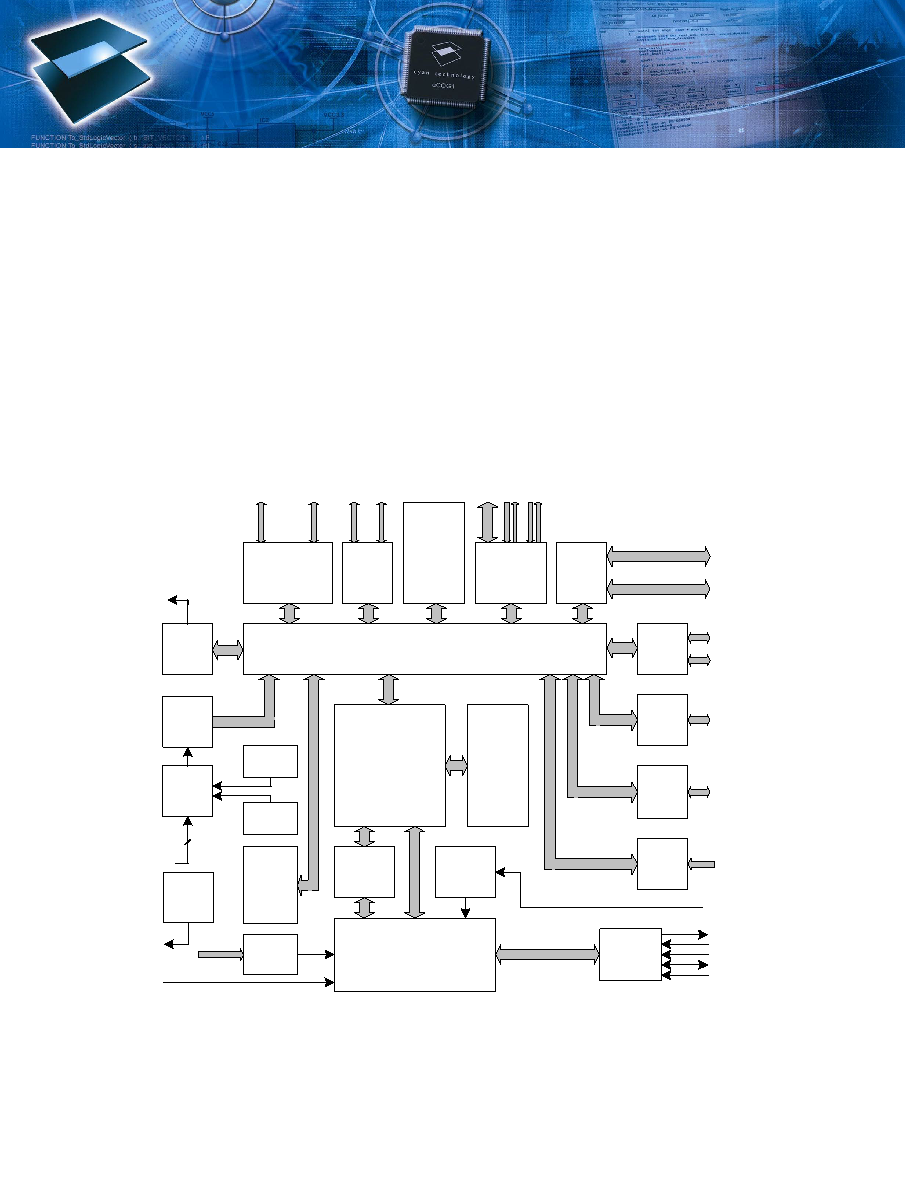

4KBytes

iRAM

Dual

UART

USART/SPI/IR

/IrDA/I2C/

Smart Card IF

IntAct

EHI

Switching Multiplexer

PWM

MMU

64K

Bytes

Flash

EPROM

Code

Cache

eCOG1

CPU Core

IRC

Temp

Sensor

EMI

PIF

GPIO

eICE

MUX

12 Bit

ADC

Power

On

Reset

eICE_miso

eICE_Clock

eICE_Load#

Interupt

Requests

Vin

Timers

System

Clock

Clock Inputs

External

Triggers

24 Bit

Addr/Data

8 Bit Data

16/32 Bit

Interface

29 Bit I/O

or Control

Up

Down

ChA

ChB

Data

Control

Vdd

Sensor

Stream

Register

Block

4

eICE_mosi

eICE_CS

Reset_In

Figure 1 – Internal Block Diagram

This document describes a device that is currently at pre-production status. Some specifications or descriptions may change.

PRELIMINARY

eCOG1 Microcontroller

Low Power Communications Processor

相关PDF资料 |

PDF描述 |

|---|---|

| ECP050 | |

| ECP100 | |

| EDGE4707B | Edge4707B PPMU Settling Time & Stability (224k) |

| EDI22AG27264V10D3 | 2x64Kx72, 3.3V Synchronous/Synchronous Burst SRAM Module(2x64Kx72, 3.3V,10ns,同步/同步脉冲静态RAM模块) |

| EDI22AG27264V12D4 | 2x64Kx72, 3.3V Synchronous/Synchronous Burst SRAM Module(2x64Kx72, 3.3V,12ns,同步/同步脉冲静态RAM模块) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ECOG1KG | 制造商:CYAN 功能描述:IC MCU 16BIT 64K FLASH 128LQFP |

| ECOG1X14B5 | 制造商:CYAN 功能描述:MCU 16BIT 512K FLASH USB/ENET 100QFN 制造商:Cyan CompanyInc 功能描述:MCU, 16BIT, 512K FLASH, USB/ENET, 100QFN |

| ECOG1X14Z5 | 制造商:CYAN 功能描述:MCU 16BIT 512K FLASH USB/ENET 208BGA 制造商:Cyan CompanyInc 功能描述:MCU, 16BIT, 512K FLASH, USB/ENET, 208BGA |

| ECOG1X1A5 | 制造商:CYAN 功能描述:MCU 16BIT 512K FLASH ADC 68QFN |

| ECOG1X5A5 | 制造商:CYAN 功能描述:MCU 16BIT 512K FLASH USB 68QFN |

发布紧急采购,3分钟左右您将得到回复。