- 您现在的位置:买卖IC网 > PDF目录10583 > EL9115ILZ-T13 (Intersil)IC ANALOG DELAY LINE TRPL 20-QFN PDF资料下载

参数资料

| 型号: | EL9115ILZ-T13 |

| 厂商: | Intersil |

| 文件页数: | 9/10页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG DELAY LINE TRPL 20-QFN |

| 标准包装: | 2,500 |

| 类型: | 视频延迟线 |

| 应用: | 模拟波速合成,失真控制 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VQFN 裸露焊盘 |

| 供应商设备封装: | 20-QFN(5x5) |

| 包装: | 带卷 (TR) |

8

FN7441.7

January 12, 2012

shifted directly to the final registers as it is clocked in. Initial

value of all registers on power-up is 0. It is the user's

responsibility to send complete patterns of 8 clock cycles,

even if the first bit is set to 1. If less than 8 bits are sent, data

will only be partially shifted through the registers. The pattern

of 8 starts with NSEnable going low, so it is good practice to

frame each word within an NS enable burst.

Test Pins

Three test pins are provided (Test R, Test G, Test B). During

normal operation, the test pins output pulses of current for a

duration of the overlap between the inputs, as shown in

Figure 15:

Test_R pulse = Red out (A) wrt Green out (B)

Test_G pulse = Green out

wrt Blue out

Test_B pulse = Blue out

wrt Red out

Averaging the current gives a direct measure of the delay

between the two edges. When A precedes B the current

pulse is +50A, and the output voltage goes up. When B

precedes A, the pulse is -50A.

For the logic to work correctly, A and B must have a period of

overlap while they are high (a delay longer than the pulse

width cannot be measured).

Signals A and B are derived from the video input by

comparing the video signal with a slicing level, which is set by

an internal DAC. This enables the delay to be measured

either from the rising edges of sync-like signals encoded on

top of the video or from a dedicated set-up signal. The outputs

can be used to set the correct delays for the signals received.

The DAC level is set through the serial input by bits 1

through 4 directed to the test register (00). Table 2 shows the

settings for the DAC slice level bits.

Test Mode

Bit zero of the test register is set to 0 for normal operation. If

it is set to 1 then the device is in Test Mode. In Test Mode,

the DAC voltage is directed to the Green channel output,

while for the Red and Blue channels, the test outputs are

now pulses of current which are generated by looking at the

delay between the input and output of the channel. They

thus enable the delay to be measured.

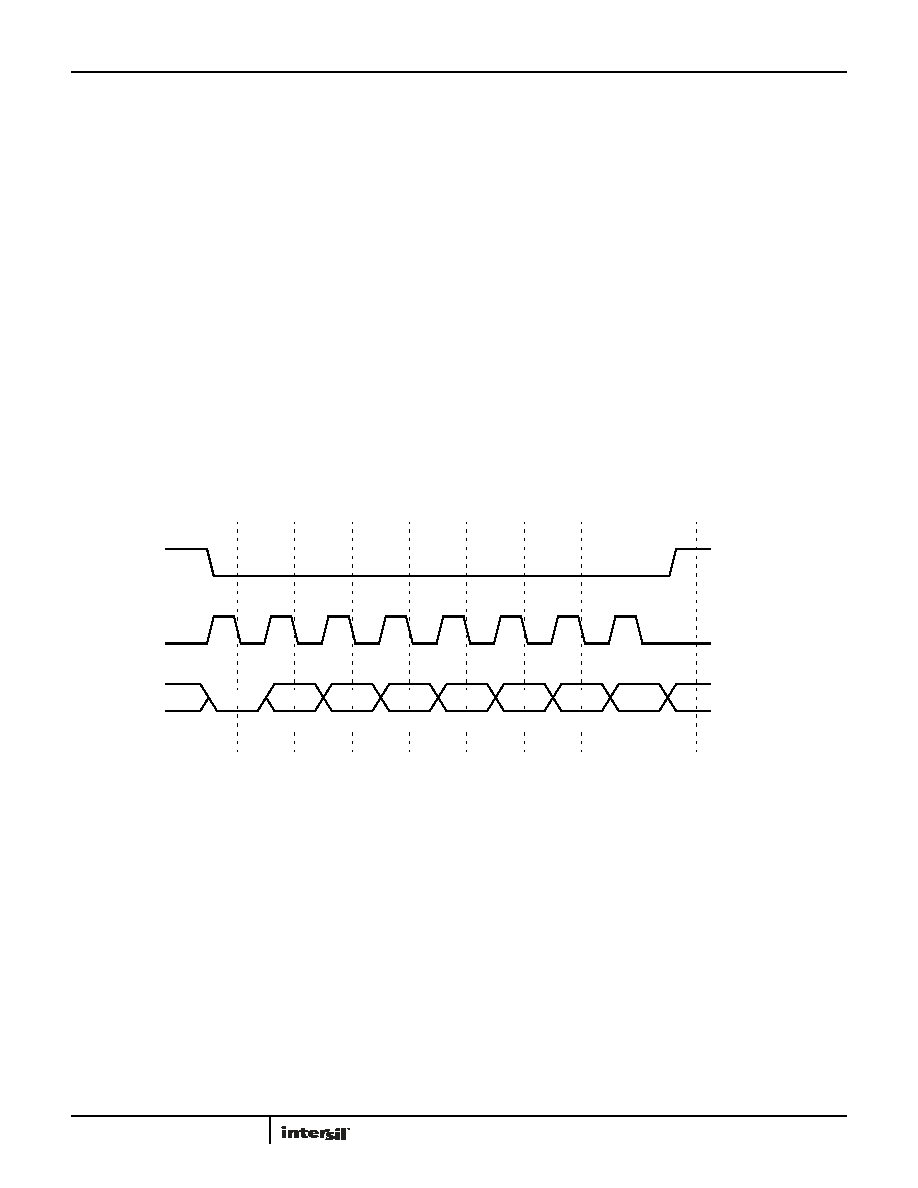

NSENABLE

SCLOCK

SDATA

A1

A0

D4

D3

D2

D1

D0

0

a

b

v

w

x

y

z

FIGURE 14. SERIAL DATA TIMING

EL9115

相关PDF资料 |

PDF描述 |

|---|---|

| SF6282-5PG-520 | CONN PLUG 5POS CABLE PIN |

| ISL59921IRZ-T7 | IC ANLG VID LINE TRPL 20-QFN |

| LTC2452CDDB#TRMPBF | IC ADC 16BIT DELTA SIG 8-DFN |

| SP211ECT-L | IC TXRX RS232 ESD LP 28WSOIC |

| ISL59923IRZ | IC ANLG VID LINE TRPL 20-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EL9115ILZ-T7 | 功能描述:延迟线/计时元素 EL9115ILZ TRPL ANLOG G VID DELAY LINE RoHS:否 制造商:Micrel 功能:Active Programmable Delay Line 传播延迟时间:1000 ps 工作温度范围: 封装 / 箱体:QFN-24 封装:Tube |

| EL-91-21SURC/S530-A2/TR10 | 功能描述:标准LED-SMD Red Water Clear 624nm 482mcd RoHS:否 制造商:Vishay Semiconductors 封装 / 箱体:0402 LED 大小:1 mm x 0.5 mm x 0.35 mm 照明颜色:Red 波长/色温:631 nm 透镜颜色/类型:Water Clear 正向电流:30 mA 正向电压:2 V 光强度:54 mcd 显示角:130 deg 系列:VLMx1500 封装:Reel |

| EL91-21-USRC/S530-A4-TR7 | 制造商:Everlight Electronics Co 功能描述: |

| EL-91-21UYC/S400-A4/TR7 | 功能描述:标准LED-SMD Yellow Water Clear GULL WING LEAD RoHS:否 制造商:Vishay Semiconductors 封装 / 箱体:0402 LED 大小:1 mm x 0.5 mm x 0.35 mm 照明颜色:Red 波长/色温:631 nm 透镜颜色/类型:Water Clear 正向电流:30 mA 正向电压:2 V 光强度:54 mcd 显示角:130 deg 系列:VLMx1500 封装:Reel |

| EL-91-21UYC/S530-A2/TR10 | 功能描述:标准LED-SMD Yellow Water Clear 589nm 496mcd RoHS:否 制造商:Vishay Semiconductors 封装 / 箱体:0402 LED 大小:1 mm x 0.5 mm x 0.35 mm 照明颜色:Red 波长/色温:631 nm 透镜颜色/类型:Water Clear 正向电流:30 mA 正向电压:2 V 光强度:54 mcd 显示角:130 deg 系列:VLMx1500 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。