- 您现在的位置:买卖IC网 > PDF目录22034 > EP1K30TC144-3N (Altera)IC ACEX 1K FPGA 30K 144-TQFP PDF资料下载

参数资料

| 型号: | EP1K30TC144-3N |

| 厂商: | Altera |

| 文件页数: | 30/86页 |

| 文件大小: | 0K |

| 描述: | IC ACEX 1K FPGA 30K 144-TQFP |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 180 |

| 系列: | ACEX-1K® |

| LAB/CLB数: | 216 |

| 逻辑元件/单元数: | 1728 |

| RAM 位总计: | 24576 |

| 输入/输出数: | 102 |

| 门数: | 119000 |

| 电源电压: | 2.375 V ~ 2.625 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-TQFP(20x20) |

| 产品目录页面: | 602 (CN2011-ZH PDF) |

| 其它名称: | 544-1839 EP1K30TC144-3N-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

36

Altera Corporation

ACEX 1K Programmable Logic Device Family Data Sheet

f For more information, search for “SameFrame” in MAX+PLUS II Help.

Note:

(1)

This option is supported with a 256-pin FineLine BGA package and SameFrame

migration.

ClockLock &

ClockBoost

Features

To support high-speed designs, -1 and -2 speed grade ACEX 1K devices

offer ClockLock and ClockBoost circuitry containing a phase-locked loop

(PLL) that is used to increase design speed and reduce resource usage. The

ClockLock circuitry uses a synchronizing PLL that reduces the clock delay

and skew within a device. This reduction minimizes clock-to-output and

setup times while maintaining zero hold times. The ClockBoost circuitry,

which provides a clock multiplier, allows the designer to enhance device

area efficiency by sharing resources within the device. The ClockBoost

feature allows the designer to distribute a low-speed clock and multiply

that clock on-device. Combined, the ClockLock and ClockBoost features

provide significant improvements in system performance and

bandwidth.

The ClockLock and ClockBoost features in ACEX 1K devices are enabled

through the Altera software. External devices are not required to use these

features. The output of the ClockLock and ClockBoost circuits is not

available at any of the device pins.

The ClockLock and ClockBoost circuitry lock onto the rising edge of the

incoming clock. The circuit output can drive the clock inputs of registers

only; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and

ClockBoost circuitry. When the dedicated clock pin is driving the

ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

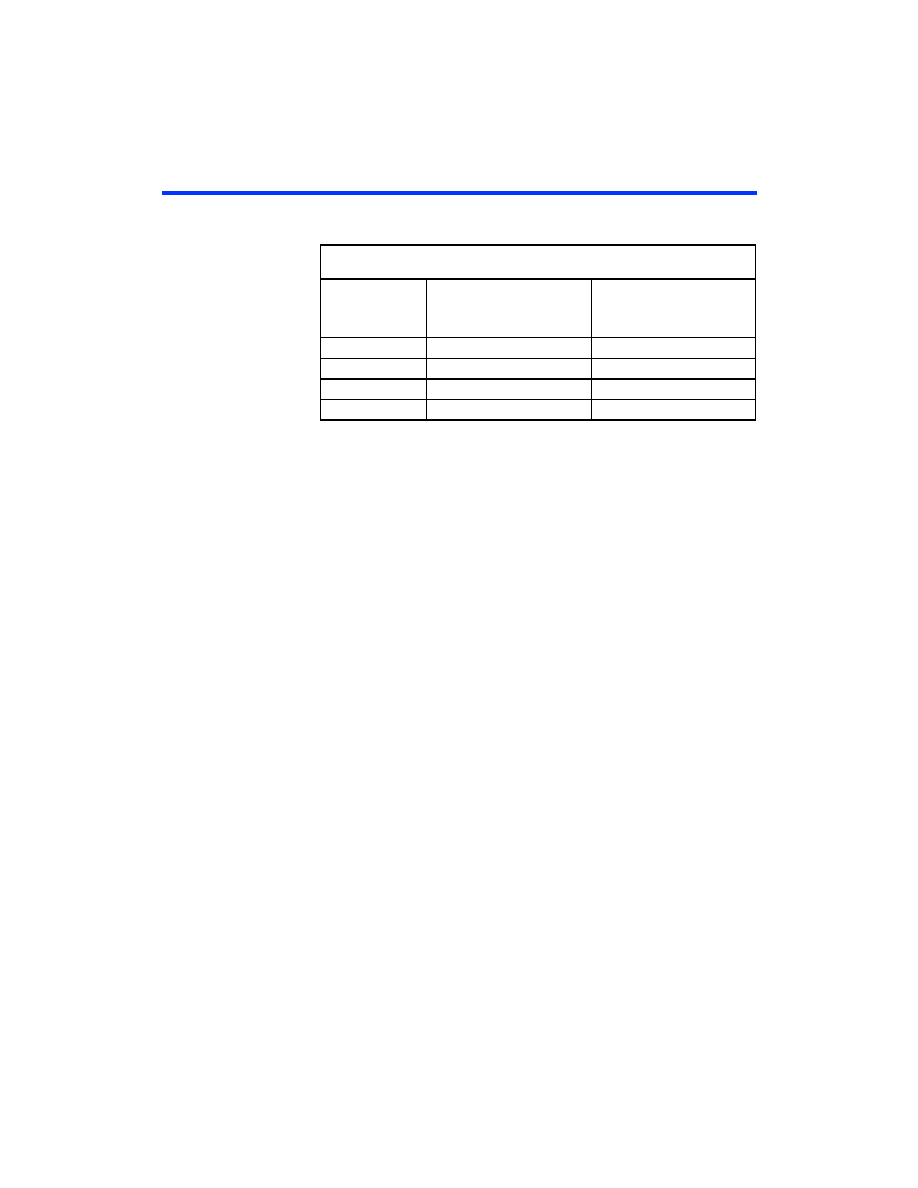

Table 10. ACEX 1K SameFrame Pin-Out Support

Device

256-Pin

FineLine

BGA

484-Pin

FineLine

BGA

EP1K10

v

EP1K30

v

EP1K50

vv

EP1K100

vv

相关PDF资料 |

PDF描述 |

|---|---|

| 7-1624113-2 | INDUCTOR 2.7UH 5% 0805 |

| EP1K30TC144-3 | IC ACEX 1K FPGA 30K 144-TQFP |

| ADT7463ARQZ-REEL7 | IC REMOTE THERMAL CTRLR 24-QSOP |

| EPF6010ATC100-3N | IC FLEX 6000 FPGA 10K 100-TQFP |

| ADT7463ARQZ | IC REMOTE THERMAL CTRLR 24-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP1K30TI144-2 | 功能描述:FPGA - 现场可编程门阵列 FPGA - ACEX 1K 216 LABs 102 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP1K30TI144-2N | 功能描述:FPGA - 现场可编程门阵列 FPGA - ACEX 1K 216 LABs 102 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP1K50 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Programmable Logic Device Family |

| EP1K50FC256-1 | 功能描述:FPGA - 现场可编程门阵列 FPGA - ACEX 1K 360 LABs 186 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP1K50FC256-1DX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。