参数资料

| 型号: | EP4SGX360FF35C2X |

| 厂商: | Altera |

| 文件页数: | 63/82页 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 360K 1152FBGA |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 3 |

| 系列: | Stratix® IV GX |

| LAB/CLB数: | 14144 |

| 逻辑元件/单元数: | 353600 |

| RAM 位总计: | 23105536 |

| 输入/输出数: | 564 |

| 电源电压: | 0.87 V ~ 0.93 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 1152-BBGA |

| 供应商设备封装: | 1152-FBGA(27x27) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页当前第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

1–58

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

Switching Characteristics

Stratix IV Device Handbook

March 2014

Altera Corporation

Volume 4: Device Datasheet and Addendum

Table 1–44 lists the DPA lock time specifications for Stratix IV GX and GT devices.

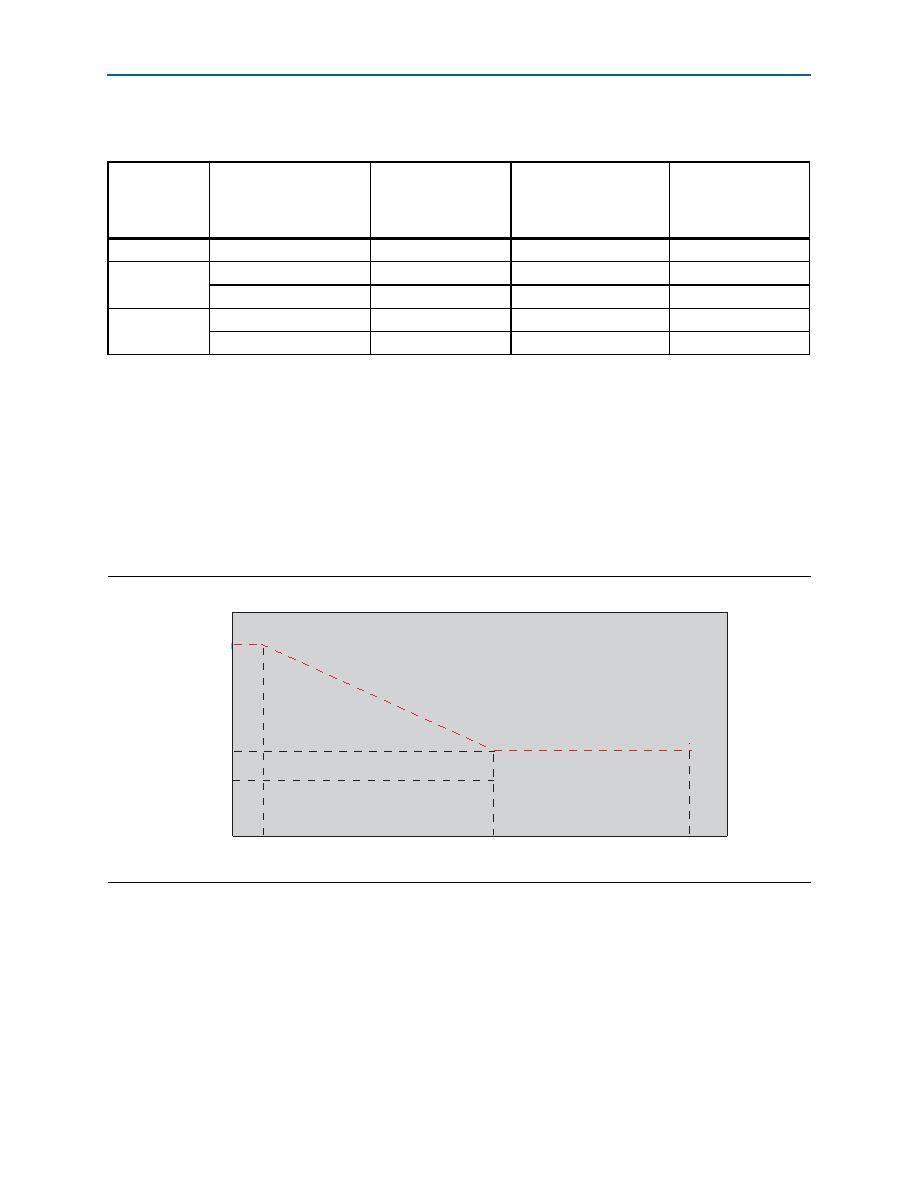

Figure 1–5 shows the LVDS soft-CDR/DPA sinusoidal jitter tolerance specification for

a data rate equal to or higher than 1.25 Gbps. Table 1–45 lists this information in table

form.

Standard

Training Pattern

Number of Data

Transitions in One

Repetition of the

Training Pattern

Number of Repetitions

per 256 Data Transitions

Maximum

SPI-4

00000000001111111111

2

128

640 data transitions

Parallel Rapid

I/O

00001111

2

128

640 data transitions

10010000

4

64

640 data transitions

Miscellaneous

10101010

8

32

640 data transitions

01010101

8

32

640 data transitions

Notes to Table 1–44:

(1) The DPA lock time is for one channel.

(2) One data transition is defined as a 0-to-1 or 1-to-0 transition.

(3) The DPA lock time stated in the table applies to commercial, industrial, and military speed grades.

(4) This is the number of repetitions for the stated training pattern to achieve the 256 data transitions.

Figure 1–5. LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate Equal to or Higher Than

1.25 Gbps

LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification

F1

F2

F3

F4

Jitter Frequency (Hz)

Jitter

Amphlit

u

de

(UI)

0.1

0.35

8.5

25

相关PDF资料 |

PDF描述 |

|---|---|

| EP2S180F1508I4N | IC STRATIX II FPGA 180K 1508FBGA |

| EP2S180F1508C3N | IC STRATIX II FPGA 180K 1508FBGA |

| EP4SGX290KF40I3 | IC STRATIX IV FPGA 290K 1517FBGA |

| 24AA024T-I/MC | IC EEPROM 2KBIT 400KHZ 8DFN |

| EP4SGX290KF40C2 | IC STRATIX IV FPGA 290K 1517FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP4SGX360FF35C2XN | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4SGX360FF35C3 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4SGX360FF35C3N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4SGX360FF35C4 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4SGX360FF35C4N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV GX 14144 LABs 564 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。