- 您现在的位置:买卖IC网 > PDF目录19911 > EPC1213LI20 (Altera)IC CONFIG DEVICE 212KBIT 20-PLCC PDF资料下载

参数资料

| 型号: | EPC1213LI20 |

| 厂商: | Altera |

| 文件页数: | 8/26页 |

| 文件大小: | 0K |

| 描述: | IC CONFIG DEVICE 212KBIT 20-PLCC |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 588 |

| 系列: | EPC |

| 可编程类型: | OTP |

| 存储容量: | 212kb |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 20-LCC(J 形引线) |

| 供应商设备封装: | 20-PLCC(9x9) |

| 包装: | 管件 |

| 配用: | PLMJ1213-ND - PROGRAMMER ADAPTER 20 PIN J-LEAD |

| 其它名称: | 544-1369-5 EPC1213LI20-ND |

Page 16

Timing Information

Configuration Devices for SRAM-Based LUT Devices

January 2012

Altera Corporation

Timing Information

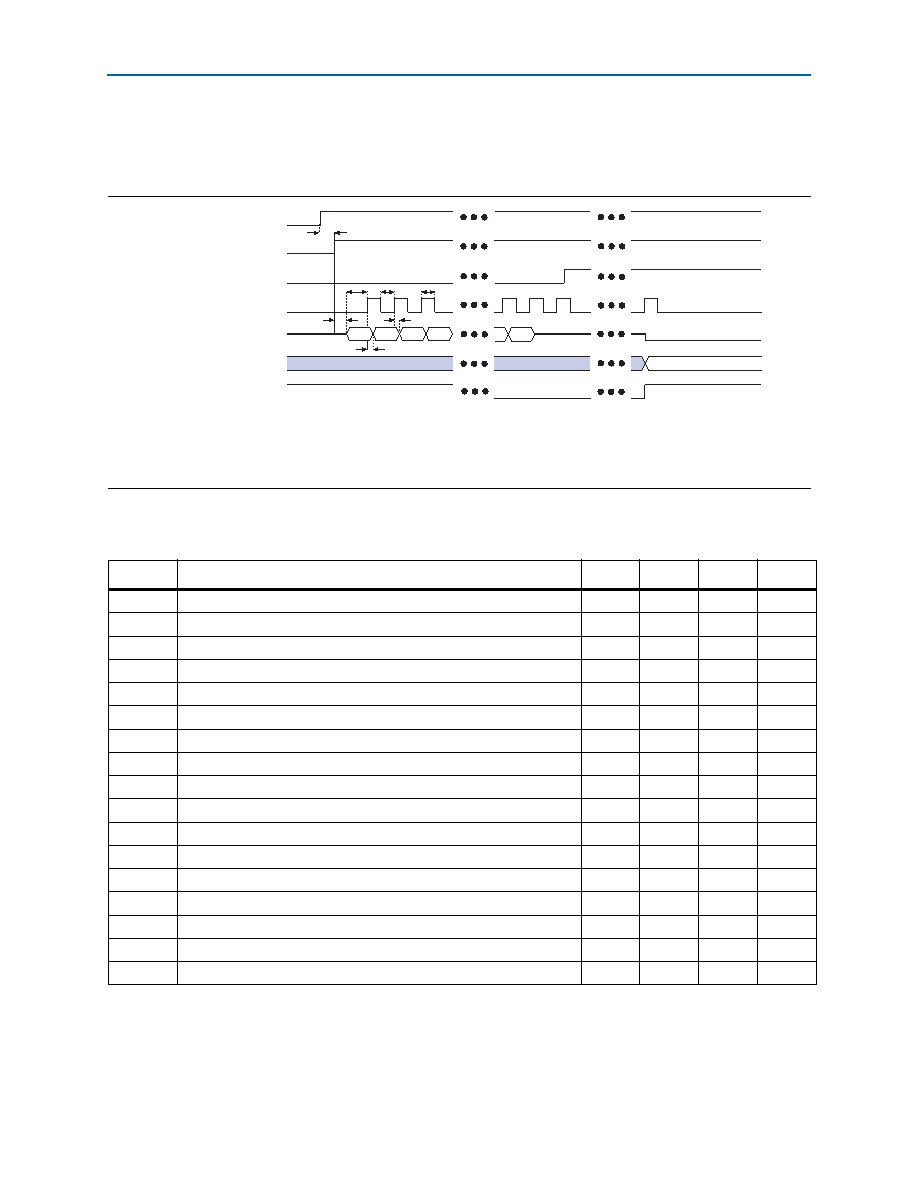

Figure 5 shows the timing waveform when using a configuration device.

Table 8 lists the timing parameters when using EPC2 devices at 3.3 V.

Figure 5. Timing Waveform Using a Configuration Device

Note to Figure 5:

(1) The EPC2 device drives DCLK low and DATA high after configuration. The EPC1 and EPC1441 devices drive DCLK low and tri-state DATA after

configuration.

DD

D

0

1

2

3

Dn

Tri-State

User Mode

(1)

tOEZX

tPOR

tCH

tCL

tDSU

tCO

tDH

Tri-State

OE/nSTATUS

nCS/CONF_DONE

DCLK

DATA

User I/O

INIT_DONE

nINIT_CONF or VCC/nCONFIG

Table 8. Timing Parameters when Using EPC2 devices at 3.3 V

Symbol

Parameter

Min

Typ

Max

Units

tPOR

POR delay (1)

——

200

ms

tOEZX

OE

high to DATA output enabled

—

80

ns

tCE

OE

high to first rising edge on DCLK

——

300

ns

tDSU

Data

setup time before rising edge on DCLK

30

—

ns

tDH

Data

hold time after rising edge on DCLK

0—

—

ns

tCO

DCLK

to DATA out

—

30

ns

tCDOE

DCLK

to DATA enable/disable

—

30

ns

fCLK

DCLK

frequency

5

7.7

12.5

MHz

tMCH

DCLK

high time for the first device in the configuration chain

40

65

100

ns

tMCL

DCLK

low time for the first device in the configuration chain

40

65

100

ns

tSCH

DCLK

high time for subsequent devices

40

—

ns

tSCL

DCLK

low time for subsequent devices

40

—

ns

tCASC

DCLK

rising edge to nCASC

—

25

ns

tCCA

nCS

to nCASC cascade delay

—

15

ns

tOEW

OE

low pulse width (reset) to guarantee counter reset

100

—

ns

tOEC

OE

low (reset) to DCLK disable delay

—

30

ns

tNRCAS

OE

low (reset) to nCASC delay

—

30

ns

Note to Table 8:

(1) During initial power-up, a POR delay occurs to permit voltage levels to stabilize. Subsequent reconfigurations do not incur this delay.

相关PDF资料 |

PDF描述 |

|---|---|

| GRM1885C2A511JA01D | CAP CER 510PF 100V 5% NP0 0603 |

| T86E227K010EBAS | CAP TANT 220UF 10V 10% 2917 |

| TAJE337K010RNJ | CAP TANT 330UF 10V 10% 2917 |

| EMC36DRXI-S734 | CONN EDGECARD 72POS DIP .100 SLD |

| EPC1213PI8 | IC CONFIG DEVICE 212KBIT 8-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPC1213LI-20 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

| EPC1213PC8 | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 212Kb 6 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC1213PC-8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

| EPC1213PI8 | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 212Kb 6 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC1213PI-8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configuration EPROM |

发布紧急采购,3分钟左右您将得到回复。