- 您现在的位置:买卖IC网 > PDF目录362753 > EPM7096LC68-12 (Altera Corporation) Programmable Logic Device Family PDF资料下载

参数资料

| 型号: | EPM7096LC68-12 |

| 厂商: | Altera Corporation |

| 英文描述: | Programmable Logic Device Family |

| 中文描述: | 可编程逻辑器件系列 |

| 文件页数: | 14/62页 |

| 文件大小: | 1173K |

| 代理商: | EPM7096LC68-12 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

14

Altera Corporation

MAX 7000 Programmable Logic Device Family Data Sheet

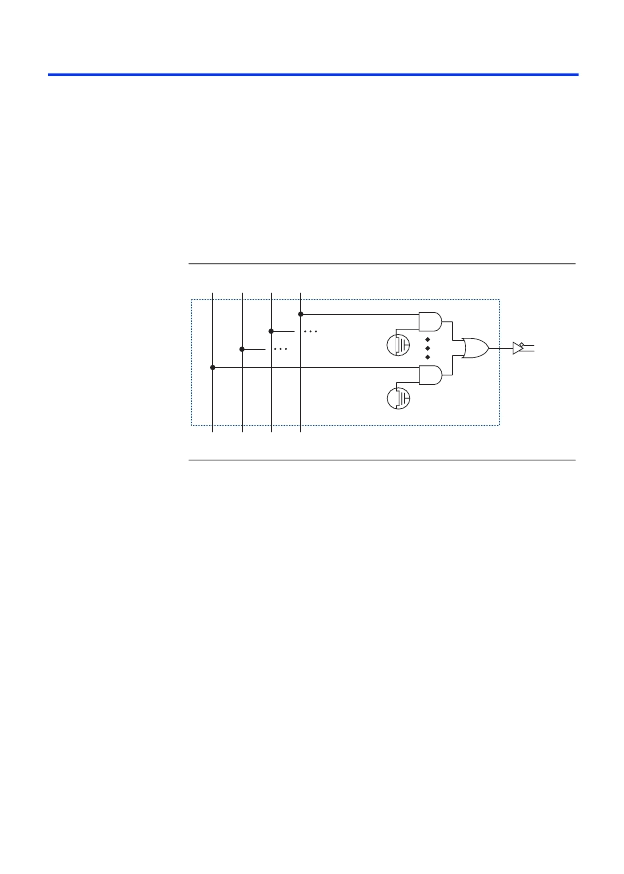

Programmable Interconnect Array

Logic is routed between LABs via the programmable interconnect array

(PIA). This global bus is a programmable path that connects any signal

source to any destination on the device. All MAX 7000 dedicated inputs,

I/ O pins, and macrocell outputs feed the PIA, which makes the signals

available throughout the entire device. Only the signals required by each

LAB are actually routed from the PIA into the LAB.

Figure7

shows how

the PIA signals are routed into the LAB. An EEPROM cell controls one

input to a 2-input

AND

gate, which selects a PIA signal to drive into the

LAB.

Figure 7. PIA Routing

While the routing delays of channel-based routing schemes in masked or

FPGAs are cumulative, variable, and path-dependent, the MAX 7000 PIA

has a fixed delay. The PIA thus eliminates skew between signals and

makes timing performance easy to predict.

I/O Control Blocks

The I/ O control block allows each I/ O pin to be individually configured

for input, output, or bidirectional operation. All I/ O pins have a tri-state

buffer that is individually controlled by one of the global output enable

signals or directly connected to ground or V

CC

.

Figure 8

shows the I/ O

control block for the MAX 7000 family. The I/ O control block of EPM7032,

EPM7064, and EPM7096 devices has two global output enable signals that

are driven by two dedicated active-low output enable pins (

OE1

and

OE2

).

The I/ O control block of MAX 7000E and MAX 7000S devices has six

global output enable signals that are driven by the true or complement of

two output enable signals, a subset of the I/ O pins, or a subset of the I/ O

macrocells.

To LAB

PIA Signals

相关PDF资料 |

PDF描述 |

|---|---|

| EPM7512AE | Programmable Logic Device Family(MAX7000A可编程逻辑系列器件) |

| EPM7256AE | Programmable Logic Device Family(MAX7000A可编程逻辑系列器件) |

| EPM9320A | Programmable Logic Device Family(MAX9000可编程逻辑系列器件) |

| EPM9480 | Programmable Logic Device Family(MAX9000可编程逻辑系列器件) |

| EPM9320 | Programmable Logic Device Family(MAX9000可编程逻辑系列器件) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM7096LC68-15 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 96 Macro 52 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7096LC68-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UV-Erasable/OTP Complex PLD |

| EPM7096LC68-3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UV-Erasable/OTP Complex PLD |

| EPM7096LC68-7 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 7000 96 Macro 52 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM7096LC84 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UV-Erasable/OTP Complex PLD |

发布紧急采购,3分钟左右您将得到回复。