- 您现在的位置:买卖IC网 > PDF目录16581 > EVAL-AD5247DBZ (Analog Devices Inc)BOARD EVAL FOR AD5247DBZ PDF资料下载

参数资料

| 型号: | EVAL-AD5247DBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/20页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD5247DBZ |

| 标准包装: | 1 |

| 系列: | * |

Data Sheet

AD5247

Rev. F | Page 5 of 20

Parameter

Symbol

Conditions

Min

Typ1

Max

Unit

DYNAMIC CHARACTERISTICS6, 8

Bandwidth –3 dB

BW

RAB = 10 k/50 k/100 k,

code = 0x40

600/100/40

kHz

Total Harmonic Distortion

THDW

VA =1 V rms, f = 1 kHz, RAB = 10 k

0.05

%

VW Settling Time (10 k/50 k/100 k)

tS

VA = 5 V ±1 LSB error band

2

s

Resistor Noise Voltage Density

eN_WB

RWB = 5 k, RS = 0

9

nV/√Hz

1

Typical specifications represent average readings at 25°C and VDD = 5 V.

2

Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic.

3

VA = VDD, wiper (VW) = no connect.

4

INL and DNL are measured at VW, with the RDAC configured as a potentiometer divider similar to a voltage output DAC. VA = VDD and VB = 0 V.

DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

5

Resistor Terminal A and Resistor Terminal W have no limitations on polarity with respect to each other.

6

Guaranteed by design, not subject to production test.

7

PDISS is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

8

All dynamic characteristics use VDD = 5 V.

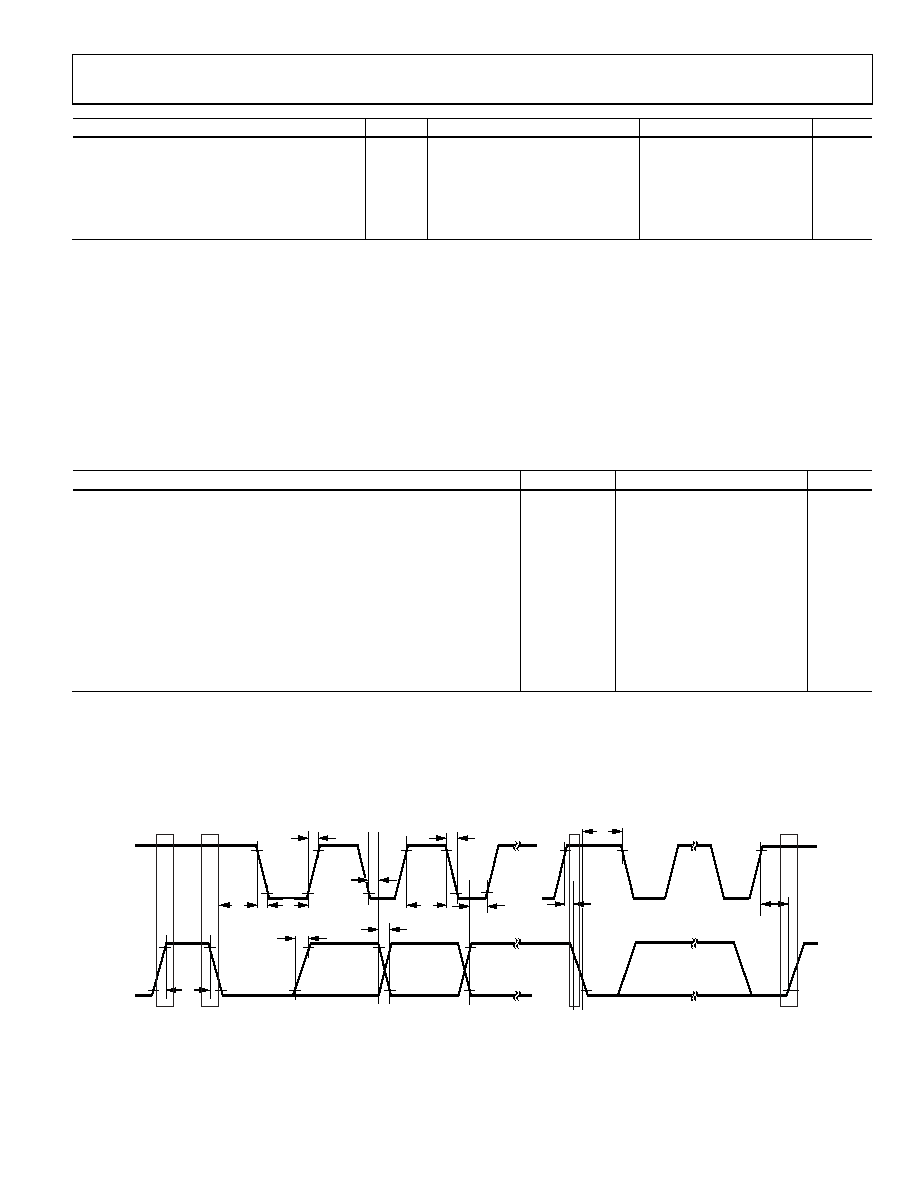

TIMING CHARACTERISTICS—5 k, 10 k, 50 k, AND 100 k VERSIONS

VDD = 5 V ± 10% or 3 V ± 10%, VA = VDD, 40°C < TA < +125°C, unless otherwise noted.

Table 3.

Parameter1, 2, 3

Symbol

Min

Typ4

Max

Unit

SCL Clock Frequency

fSCL

400

kHz

Bus Free Time Between Stop and Start, tBUF

t1

1.3

s

Hold Time (Repeated Start), tHD;STA5

t2

0.6

s

Low Period of SCL Clock, tLOW

t3

1.3

s

High Period of SCL Clock, tHIGH

t4

0.6

50

s

Setup Time for Repeated Start Condition, tSU;STA

t5

0.6

s

Data Hold Time, tHD;DAT

t6

0.9

s

Data Setup Time, tSU;DAT

t7

100

ns

Fall Time of Both SDA and SCL Signals, tF

t8

300

ns

Rise Time of Both SDA and SCL Signals, tR

t9

300

ns

Setup Time for Stop Condition, tSU;STO

t10

0.6

s

1

Specifications apply to all parts.

2

Guaranteed by design, not subject to production test.

3

4

Typical specifications represent average readings at 25°C and VDD = 5 V.

5

After this period, the first clock pulse is generated.

t7

t8

t9

P

S

P

S

t10

t5

t9

t8

SCL

SDA

t6

03876-

031

t1

t2

t3

t4

t2

Figure 2. I2C Interface, Detailed Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| EEM43DSEN-S13 | CONN EDGECARD 86POS .156 EXTEND |

| CI100505-82NJ | INDUCTOR MULTI LAYER CHIP 82NH |

| CI160808-1N0D | INDUCTOR MULTI LAYER CHIP 1.0NH |

| EEM43DSEH-S13 | CONN EDGECARD 86POS .156 EXTEND |

| GBM24DRTI | CONN EDGECARD 48POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5252EBZ | 功能描述:BOARD EVAL FOR AD5252 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| EVAL-AD5252SDZ | 功能描述:BOARD EVAL FOR AD5252 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD5254EBZ | 制造商:Analog Devices 功能描述:EVALUATION BOARD - Boxed Product (Development Kits) |

| EVAL-AD5254SDZ | 功能描述:BOARD EVAL FOR AD5254 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-AD5258DBZ | 功能描述:BOARD EVAL FOR AD5258DBZ RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。