- 您现在的位置:买卖IC网 > PDF目录17104 > EVAL-AD5764EBZ (Analog Devices Inc)BOARD EVAL FOR AD5764 PDF资料下载

参数资料

| 型号: | EVAL-AD5764EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD5764 |

| 产品培训模块: | DAC Architectures |

| 标准包装: | 1 |

| DAC 的数量: | 4 |

| 位数: | 16 |

| 采样率(每秒): | 30M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 设置时间: | 8µs |

| DAC 型: | 电压 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板,缆线,CD |

| 已用 IC / 零件: | AD5764 |

| 相关产品: | AD5764CSUZ-REEL7-ND - IC DAC 16BIT QUAD BIPO 32-TQFP AD5764BSUZ-REEL7-ND - IC DAC 16BIT QUAD VOUT 32-TQFP AD5764ASUZ-REEL7-ND - IC DAC 16BIT QUAD VOUT 32-TQFP AD5764BSUZ-ND - IC DAC 16BIT QUAD VOUT 32-TQFP AD5764ASUZ-ND - IC DAC 16BIT QUAD VOUT 32-TQFP AD5764CSUZ-ND - IC DAC 16BIT QUAD VOUT 32TQFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

AD5764

Rev. F | Page 19 of 28

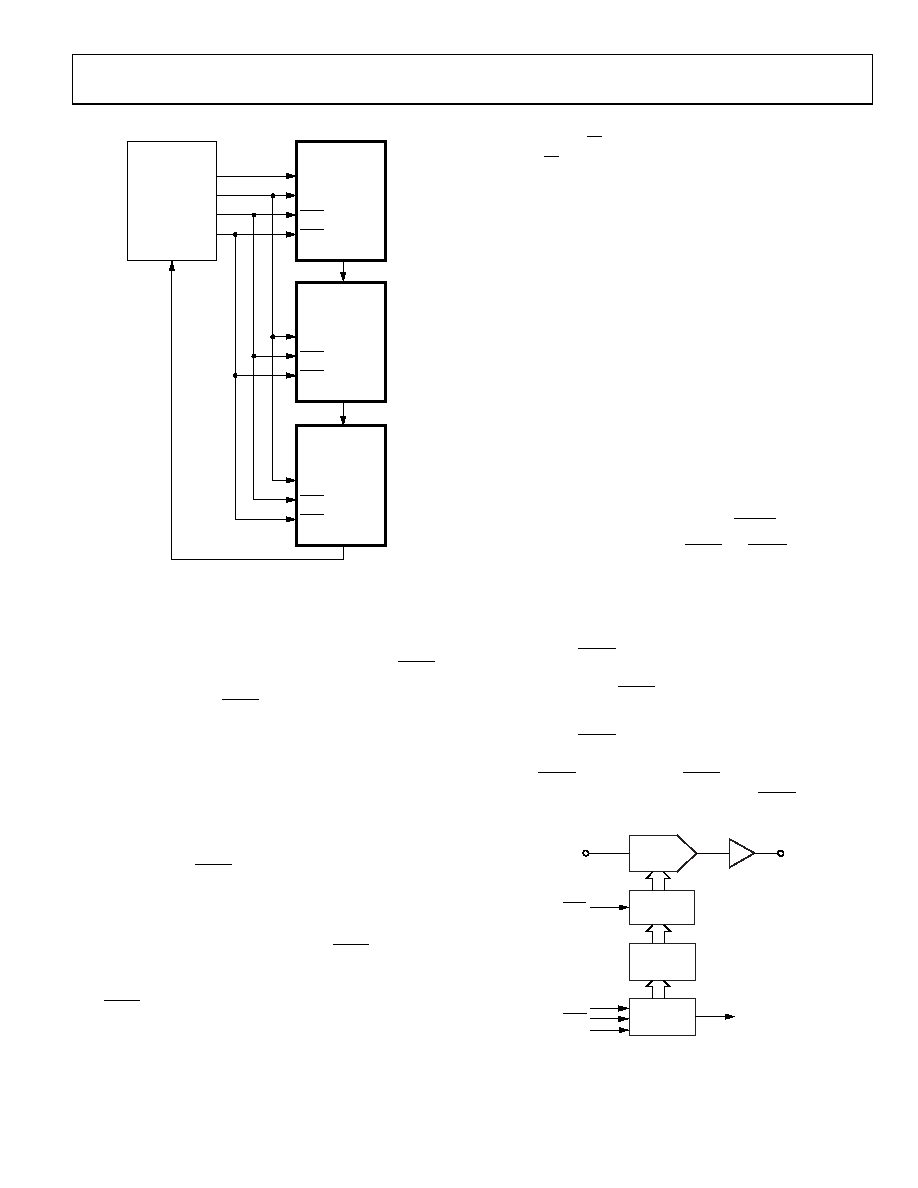

Daisy-Chain Operation

05

30

3-

06

1

68HC111

MISO

SYNC

SDIN

SCLK

MOSI

SCK

PC7

PC6

LDAC

SDO

SYNC

SCLK

LDAC

SDO

SYNC

SCLK

LDAC

SDO

SDIN

1ADDITIONAL PINS OMITTED FOR CLARITY

AD57641

Figure 33. Daisy-Chaining the AD5764

For systems that contain several devices, the SDO pin can be

used to daisy-chain several devices together. This daisy-chain

mode can be useful in system diagnostics and in reducing the

number of serial interface lines. The first falling edge of SYNC

starts the write cycle. The SCLK is continuously applied to the

input shift register when SYNC is low. If more than 24 clock

pulses are applied, the data ripples out of the input shift register

and appears on the SDO line. This data is clocked out on the

rising edge of SCLK and is valid on the falling edge. By connect-

ing the SDO of the first device to the SDIN input of the next device

in the chain, a multidevice interface is constructed. Each device in

the system requires 24 clock pulses. Therefore, the total number of

clock cycles must equal 24N, where N is the total number of

AD5764 devices in the chain. When the serial transfer to all

devices is complete, SYNC is taken high. This latches the input

data in each device in the daisy chain and prevents any further

data from being clocked into the input shift register. The serial

clock can be a continuous or a gated clock.

A continuous SCLK source can only be used if SYNC is held low

for the correct number of clock cycles. In gated clock mode, a burst

clock containing the exact number of clock cycles must be used,

and SYNC must be taken high after the final clock to latch the data.

Readback Operation

Before a readback operation is initiated, the SDO pin must be

enabled by writing to the function register and clearing the SDO

disable bit; this bit is cleared by default. Readback mode is invoked

by setting the R/W bit = 1 in the serial input shift register write.

With R/W = 1, Bit A2 to Bit A0, in association with Bit REG2,

Bit REG1, and Bit REG0, select the register to be read. The

remaining data bits in the write sequence are don’t cares. During

the next SPI write, the data appearing on the SDO output

contain the data from the previously addressed register. For a

read of a single register, the NOP command can be used in

clocking out the data from the selected register on SDO. The

readback diagram in

shows the readback sequence. For

example, to read back the fine gain register of Channel A on the

AD5764, implement the following:

1.

Write 0xA0XXXX to the AD5764 input shift register. This

configures the AD5764 for read mode with the fine gain

register of Channel A selected. Note that all the data bits,

DB15 to DB0, are don’t cares.

2.

Follow this with a second write, an NOP condition,

0x00XXXX. During this write, the data from the fine gain

register is clocked out on the SDO line, that is, data clocked

out contain the data from the fine gain register in Bit DB5

to Bit DB0.

SIMULTANEOUS UPDATING VIA LDAC

Depending on the status of both SYNC and LDAC, and after

data has been transferred into the input register of the DACs,

there are two ways in which the data register and DAC outputs

can be updated.

Individual DAC Updating

In this mode, LDAC is held low while data is being clocked into

the input shift register. The addressed DAC output is updated

on the rising edge of SYNC.

Simultaneous Updating of All DACs

In this mode, LDAC is held high while data is being clocked

into the input shift register. All DAC outputs are updated by

taking LDAC low any time after SYNC has been taken high.

The update now occurs on the falling edge of LDAC.

VOUTx

DATA

REGISTER

INTERFACE

LOGIC

OUTPUT

I/V AMPLIFIER

LDAC

SDO

SDIN

16-BIT

DAC

VREFIN

SYNC

INPUT

REGISTER

SCLK

05

30

3-

0

62

Figure 34. Simplified Serial Interface of Input Loading Circuitry

for One DAC Channel

相关PDF资料 |

PDF描述 |

|---|---|

| RSM06DTKH | CONN EDGECARD 12POS DIP .156 SLD |

| REF192GSZ-REEL7 | IC VREF SERIES PREC 2.5V 8-SOIC |

| EVAL-AD5542ASDZ | BOARD EVAL FOR AD5542 |

| EVAL-AD5541ASDZ | BOARD EVAL FOR AD5541 |

| PLG1C331MCO1 | CAP ALUM 330UF 16V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5764REBZ | 功能描述:EVAL BOARD FOR AD5764 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5765EBZ | 功能描述:BOARD EVAL FOR AD5765 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5780SDZ | 功能描述:BOARD EVALUATION FOR AD5780 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5781SDZ | 功能描述:BOARD EVAL FOR AD5781 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5790SDZ | 制造商:Analog Devices 功能描述:AD5790 DAC EVALUATION BOARD 制造商:Analog Devices 功能描述:AD5790, DAC, EVALUATION BOARD 制造商:Analog Devices 功能描述:AD5790, DAC, EVALUATION BOARD, Silicon Manufacturer:Analog Devices, Silicon Core 制造商:Analog Devices 功能描述:AD5790, DAC, EVALUATION BOARD, Silicon Manufacturer:Analog Devices, Silicon Core Number:(Not Applicable), Kit Application Type:(Not Available), Application Sub Type:DAC, Features:20-bit Voltage Output DAC, Integrated Precision , RoHS Compliant: Yes |

发布紧急采购,3分钟左右您将得到回复。