- 您现在的位置:买卖IC网 > PDF目录17048 > EVAL-AD7276SDZ (Analog Devices Inc)BOARD EVAL FOR AD7276 PDF资料下载

参数资料

| 型号: | EVAL-AD7276SDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/29页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD7276 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 3M |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ 3.6 V |

| 在以下条件下的电源(标准): | 19.8mW @ 3MSPS,3.6 V |

| 工作温度: | -40°C ~ 125°C |

| 已用 IC / 零件: | AD7276 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD7276/AD7277/AD7278

Rev. C | Page 22 of 28

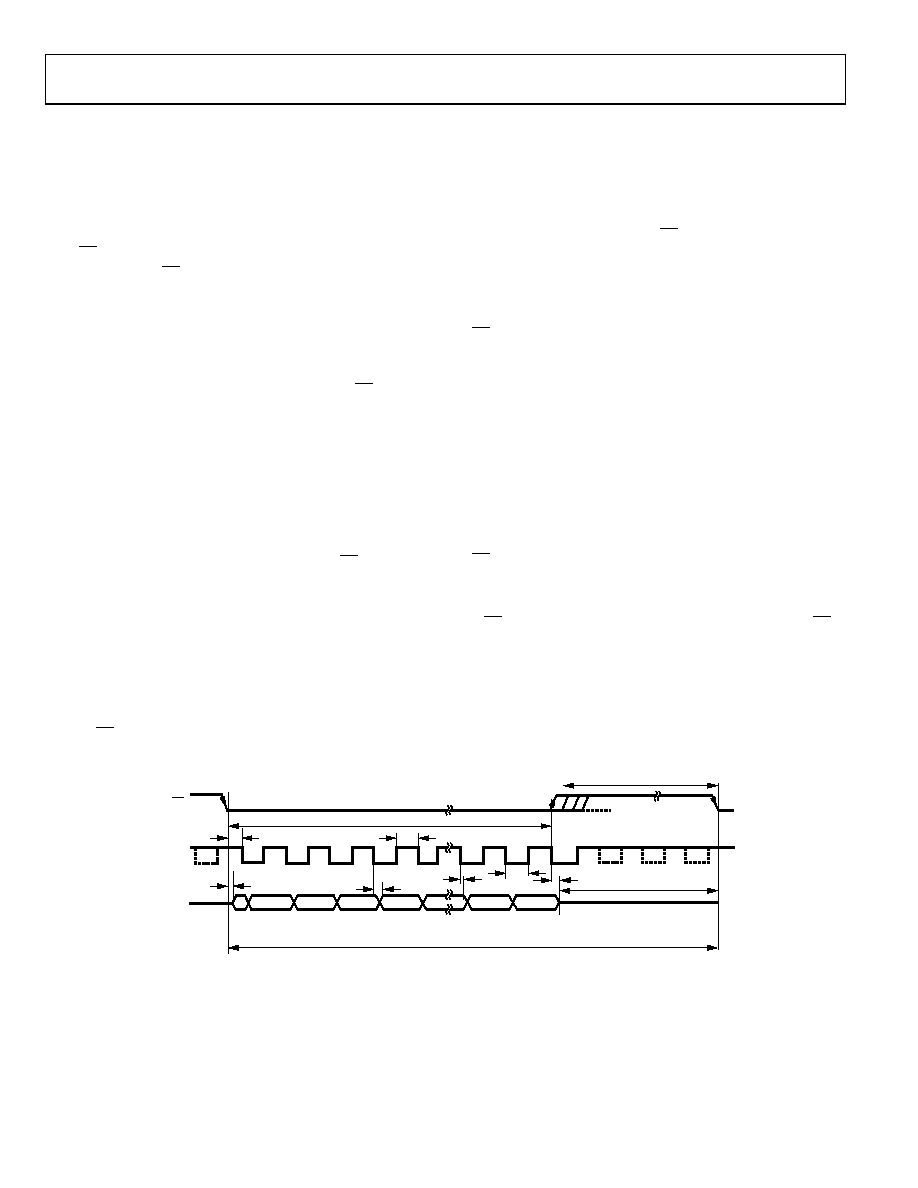

SERIAL INTERFACE

for serial interfacing to the AD7276, AD7277, and AD7278. The

serial clock provides the conversion clock and controls the transfer

of information from the AD7276/AD7277/AD7278 during

conversion.

The CS signal initiates the data transfer and conversion process.

The falling edge of CS puts the track-and-hold into hold mode

and takes the bus out of three-state. The analog input is sampled

and the conversion is initiated at this point.

For the AD7276, the conversion requires completing 14 SCLK

cycles. Once 13 SCLK falling edges have elapsed, the track-and-

hold goes back into track mode on the next SCLK rising edge,

as shown in Figure 31 at Point B. If the rising edge of CS occurs

before 14 SCLKs have elapsed, the conversion is terminated and

the SDATA line goes back into three-state. If 16 SCLKs are

considered in the cycle, the last two bits are zeros and SDATA

returns to three-state on the 16th SCLK falling edge, as shown in

.

For the AD7277, the conversion requires completing 12 SCLK

cycles. Once 11 SCLK falling edges elapse, the track-and-hold

goes back into track mode on the next SCLK rising edge, as

shown in Figure 33 at Point B. If the rising edge of CS occurs

before 12 SCLKs elapse, the conversion is terminated and the

SDATA line goes back into three-state. If 16 SCLKs are considered

in the cycle, the AD7277 clocks out four trailing zeros for the

last four bits and SDATA returns to three-state on the 16th SCLK

falling edge, as shown in

.

For the AD7278, the conversion requires completing 10 SCLK

cycles. Once 9 SCLK falling edges elapse, the track-and-hold

goes back into track mode on the next rising edge. If the rising

edge of CS occurs before 10 SCLKs elapse, the part enters power-

down mode.

If 16 SCLKs are considered in the cycle, then the AD7278 clocks

out six trailing zeros for the last six bits and SDATA returns to

If the user considers a 14 SCLK cycle serial interface for the

AD7276/AD7277/AD7278, then CS must be brought high after

the 14th SCLK falling edge. Then the last two trailing zeros are

ignored, and SDATA goes back into three-state. In this case, the

3 MSPS throughput can be achieved by using a 48 MHz clock

frequency.

CS going low clocks out the first leading zero to be read by the

microcontroller or DSP. The remaining data is then clocked out

by subsequent SCLK falling edges, beginning with the second

leading zero. Therefore, the first falling clock edge on the serial

clock provides the first leading zero and clocks out the second

leading zero. The final bit in the data transfer is valid on the 16th

falling edge, because it is clocked out on the previous (15th)

falling edge.

In applications with a slower SCLK, it is possible to read data on

each SCLK rising edge. In such cases, the first falling edge of SCLK

clocks out the second leading zero and can be read on the first

rising edge. However, the first leading zero clocked out when

CS goes low is missed if read within the first falling edge. The

15th falling edge of SCLK clocks out the last bit and can be read

on the 15th rising SCLK edge.

If CS goes low just after one SCLK falling edge elapses, then CS

clocks out the first leading zero and can be read on the SCLK

rising edge. The next SCLK falling edge clocks out the second

leading zero and can be read on the following rising edge.

04

90

3-

0

99

tQUIET

tCONVERT

1/THROUGHPUT

CS

15

13

t4

23

4

t5

t3

t2

t6

t7

t9

14

B

t1

SCLK

SDATA

THREE-STATE

THREE-

STATE

2 LEADING

ZEROS

ZZERO

DB11

DB10

DB9

DB1

DB0

Figure 31. AD7276 Serial Interface Timing Diagram 14 SCLK Cycle

相关PDF资料 |

PDF描述 |

|---|---|

| ABC05DRYS | CONN EDGECARD 10POS .100 DIP SLD |

| ESC06DREI-S734 | CONN EDGECARD 12POS .100 EYELET |

| EBC12DREI-S734 | CONN EDGECARD 24POS .100 EYELET |

| ABC07DRXN | CONN EDGECARD 14POS .100 DIP SLD |

| 0210490903 | CABLE JUMPER 1.25MM .076M 21POS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7277CB | 制造商:Analog Devices 功能描述:EVAL BD 3 MSPS, 12-/10-/8BIT ADCS IN 6-LEAD TSOT - Bulk |

| EVAL-AD7280AEDZ | 功能描述:BOARD EVAL FOR AD7280 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| EVAL-AD7291SDZ | 功能描述:BOARD EVAL FOR AD7291 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7292SDZ | 功能描述:数据转换 IC 开发工具 EVALUATION BOARD RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| EVAL-AD7294EBZ | 功能描述:BOARD EVALUATION FOR AD7294 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。