- 您现在的位置:买卖IC网 > PDF目录17031 > EVAL-AD7654CBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7654 PDF资料下载

参数资料

| 型号: | EVAL-AD7654CBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7654 |

| 标准包装: | 1 |

| 系列: | PulSAR® |

| ADC 的数量: | 2 |

| 位数: | 16 |

| 采样率(每秒): | 500k |

| 数据接口: | 串行,并联 |

| 输入范围: | 0 ~ 5 V |

| 在以下条件下的电源(标准): | 120mW @ 500kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7654 |

| 已供物品: | 板 |

| 相关产品: | AD7654ACPZ-ND - IC ADC 16BIT DUAL 2CH 48-LFCSP AD7654ASTZRL-ND - IC ADC 16BIT DUAL 2CH 48LQFP AD7654ACPZRL-ND - IC ADC 16BIT DUAL 2CH 48LFCSP AD7654ASTZ-ND - IC ADC 16BIT 500KSPS DUAL 48LQFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页

AD7654

Rev. B | Page 5 of 28

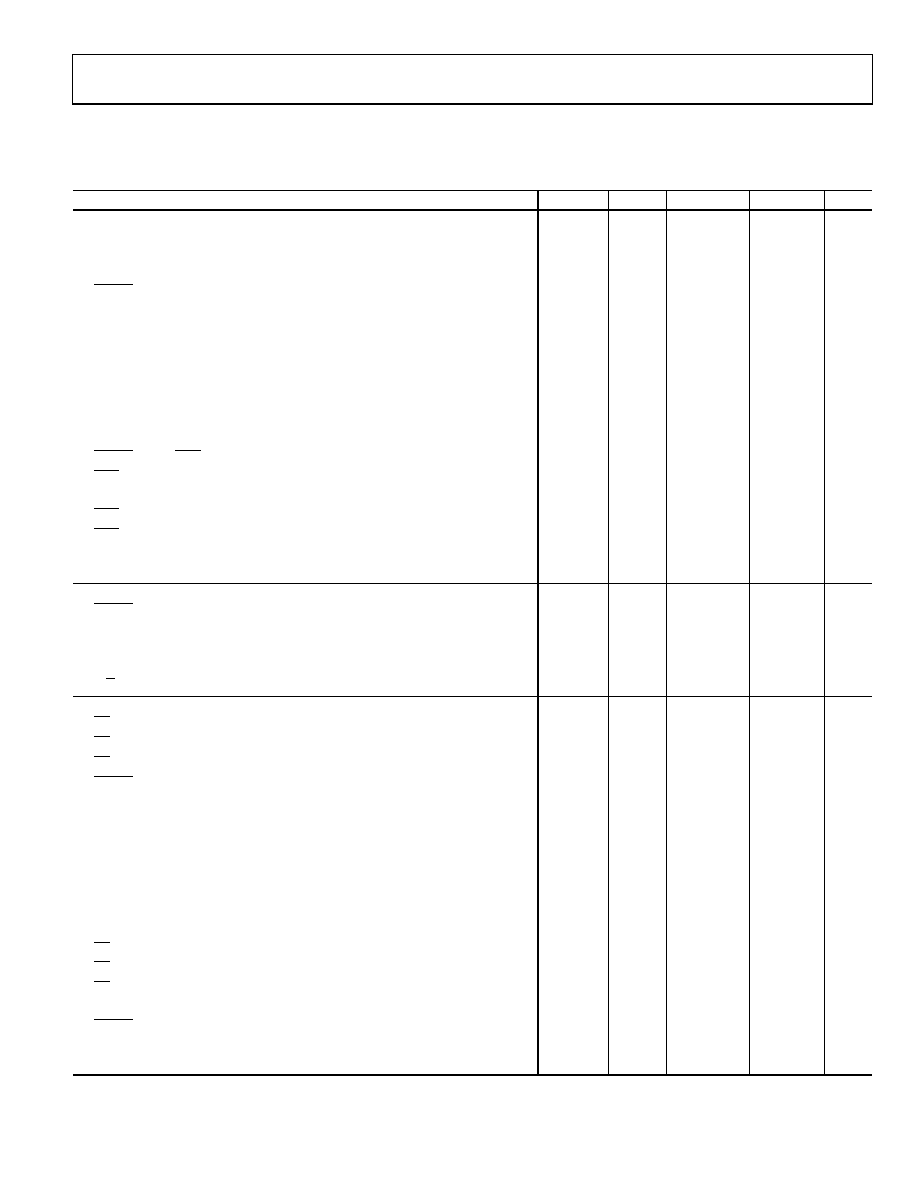

TIMING SPECIFICATIONS

AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V; all specifications TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter

Symbol

Min

Typ

Max

Unit

Convert Pulse Width

t1

5

ns

Time Between Conversions

(Normal Mode/Impulse Mode)

t2

2/2.25

μs

CNVST Low to BUSY High Delay

t3

32

ns

BUSY High All Modes Except in Master Serial Read After Convert Mode

(Normal Mode/Impulse Mode)

t4

1.75/2

μs

Aperture Delay

t5

2

ns

End of Conversions to BUSY Low Delay

t6

10

ns

Conversion Time

(Normal Mode/Impulse Mode)

t7

1.75/2

μs

Acquisition Time

t8

250

ns

RESET Pulse Width

t9

10

ns

CNVST Low to EOC High Delay

t10

30

ns

EOC High for Channel A Conversion

(Normal Mode/Impulse Mode)

t11

1/1.25

μs

EOC Low after Channel A Conversion

t12

45

ns

EOC High for Channel B Conversion

t13

0.75

μs

Channel Selection Setup Time

t14

250

ns

Channel Selection Hold Time

t15

30

ns

CNVST Low to DATA Valid Delay

t16

1.75/2

μs

DATA Valid to BUSY Low Delay

t17

14

ns

Bus Access Request to DATA Valid

t18

40

ns

Bus Relinquish Time

t19

5

15

ns

A/B Low to Data Valid Delay

t20

40

ns

CS Low to SYNC Valid Delay

t21

10

ns

CS Low to Internal SCLK Valid Delay1

t22

10

ns

CS Low to SDOUT Delay

t23

10

ns

CNVST Low to SYNC Delay (Read During Convert)

(Normal Mode/Impulse Mode)

t24

250/500

ns

SYNC Asserted to SCLK First Edge Delay

t25

3

ns

t26

23

40

ns

Internal SCLK High2

t27

12

ns

Internal SCLK Low2

t28

7

ns

SDOUT Valid Setup Time2

t29

4

ns

SDOUT Valid Hold Time2

t30

2

ns

SCLK Last Edge to SYNC Delay2

t31

1

ns

CS High to SYNC HI-Z

t32

10

ns

CS High to Internal SCLK HI-Z

t33

10

ns

CS High to SDOUT HI-Z

t34

10

ns

BUSY High in Master Serial Read After Convert2

t35

See Table 4

CNVST Low to SYNC Asserted Delay

(Normal Mode/Impulse Mode)

t36

0.75/1

μs

SYNC Deasserted to BUSY Low Delay

t37

25

ns

相关PDF资料 |

PDF描述 |

|---|---|

| STD17W-P | WIRE & CABLE MARKERS |

| EVAL-AD7653CBZ | BOARD EVALUATION FOR AD7653 |

| MLG1005S30NJ | INDUCTOR MULTILAYER 30NH 0402 |

| EVAL-AD7643CBZ | BOARD EVALUATION FOR AD7643 |

| STD17W-C | WIRE & CABLE MARKERS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7655CB | 制造商:Analog Devices 功能描述:Evaluation Board For The 48 Lead Pulsar Analog To Digital Converter Family 制造商:Rochester Electronics LLC 功能描述:EVAL BRD LOW COST 4-CH 1 MSPS 16-BIT ADC - Bulk |

| EVAL-AD7655CBZ | 功能描述:BOARD EVALUATION FOR AD7655 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:PulSAR® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7655EDZ | 功能描述:BOARD EVAL FOR AD7655 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7656-1CBZ | 功能描述:BOARD EVAL FOR AD7656-1 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:iCMOS® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7656-1EDZ | 功能描述:BOARD EVAL CONTROL AD7656-1 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:iCMOS® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。